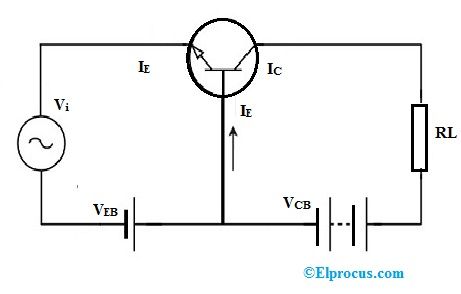

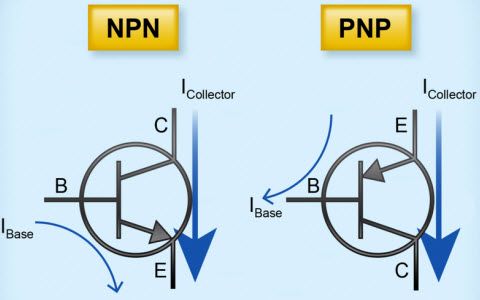

Een configuratie waarin een bipolaire junctie-transistor of een BJT is versterkt met een emitterweerstand om de stabiliteit te verbeteren met betrekking tot veranderende omgevingstemperaturen, wordt een emitter-gestabiliseerde bias-schakeling genoemd voor BJT.

We hebben al bestudeerd wat is DC-voorspanning in transistors , laten we nu verder gaan en leren hoe een emitterweerstand kan worden gebruikt om de stabiliteit van een BJT DC-biasnetwerk te verbeteren.

Emitter Gestabiliseerd Bias Circuit toepassen

De opname van de emitterweerstand in de DC-voorspanning van de BJT levert superieure stabiliteit, wat betekent dat de DC-instelstromen en -spanningen steeds dichter bij de plaats blijven waar ze waren vastgesteld door het circuit, rekening houdend met externe parameters, zoals variaties in temperatuur, en transistor beta (winst),

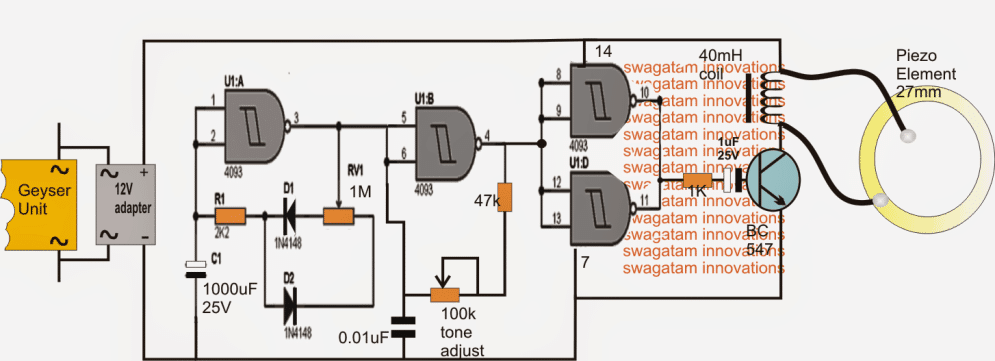

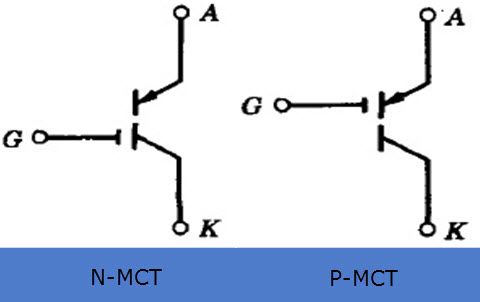

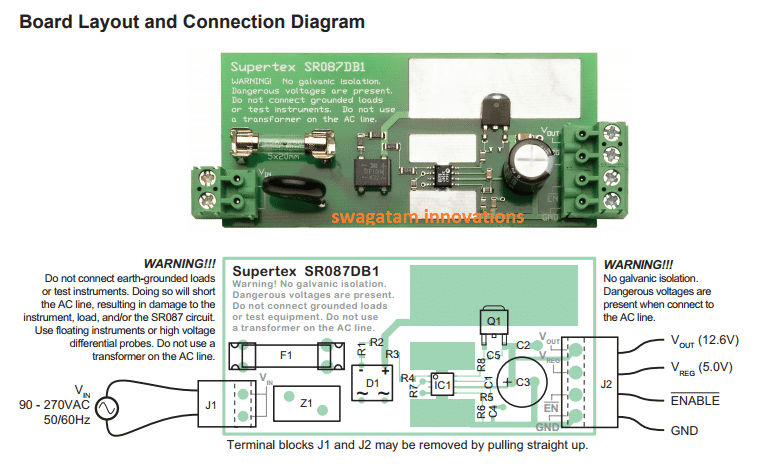

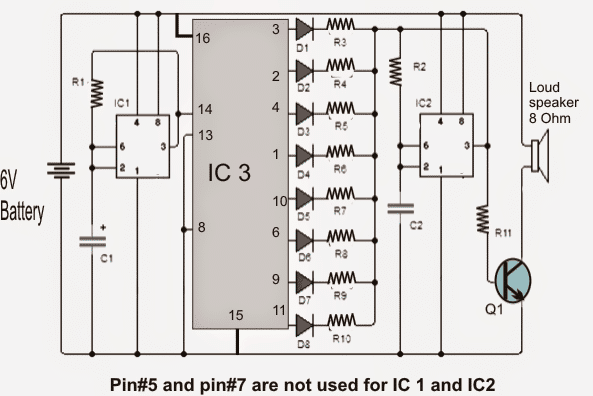

De onderstaande afbeelding toont een transistor DC-biasnetwerk met een emitterweerstand voor het afdwingen van een emitter-gestabiliseerde voorspanning op de bestaande vaste instelconfiguratie van de BJT.

Afbeelding 4.17 BJT-biascircuit met emitterweerstand

In onze besprekingen beginnen we onze analyse van het ontwerp door eerst de lus rond het basis-emittergebied van het circuit te inspecteren en vervolgens de resultaten te gebruiken om de lus rond de collector-emitterzijde van het circuit verder te onderzoeken.

Basis-emitterlus

We kunnen de bovenstaande basis-emitterlus opnieuw tekenen op de manier die hieronder wordt getoond in figuur 4.18, en als we dit toepassen De spanningswet van Kirchhoff op deze lus met de klok mee, helpt ons om de volgende vergelijking te krijgen:

+ Vcc = IBRB - VBE - IERE = 0 ------- (4.15)

Uit onze eerdere discussies weten we dat: IE = (β + 1) B. ------- (4.16)

Het vervangen van de waarde van IE in vergelijking (4.15) levert het volgende resultaat op:

Vcc = IBRB - VBE - (β + 1) IBRE = 0

Het plaatsen van de termen in hun respectievelijke groepen levert het volgende op:

Als je je herinnert uit onze vorige hoofdstukken, is de fixed bias-vergelijking afgeleid in de volgende vorm:

Als we deze fixed bias-vergelijking vergelijken met de (4.17) -vergelijking, vinden we dat het enige verschil tussen de twee vergelijkingen voor de huidige IB de term is (β + 1) RE.

Wanneer de vergelijking 4.17 wordt gebruikt voor het tekenen van een op serie gebaseerde configuratie, kunnen we een interessant resultaat extraheren, dat eigenlijk vergelijkbaar is met vergelijking 4.17.

Neem het voorbeeld van het volgende netwerk in figuur 4.19:

Als we het systeem voor de huidige IB oplossen, resulteert dit in dezelfde vergelijking als verkregen in Vgl. 4.17. Merk op dat naast de spanning van basis naar emitter VBE, de weerstand RE opnieuw te zien was aan de ingang van het basiscircuit door een niveau (β + 1).

Dit betekent dat de emitterweerstand die deel uitmaakt van de collector-emitterlus wordt weergegeven als (β + 1) RE in de basis-emitterlus.

Ervan uitgaande dat β voor de meeste BJT's meestal boven de 50 kan zijn, zou de weerstand bij de emitter van de transistors aanzienlijk groter kunnen zijn in het basiscircuit. Daarom zijn we in staat om de volgende algemene vergelijking af te leiden voor figuur 4.20:

Ri = (β + 1) RE ------ (4.18)

U zult deze vergelijking best handig vinden bij het oplossen van veel toekomstige netwerken. In feite maakt deze vergelijking het gemakkelijker om vergelijking 4.17 op een gemakkelijkere manier te onthouden.

Volgens de wet van Ohm weten we dat de stroom door een netwerk de spanning is gedeeld door de weerstand van het circuit.

De spanning voor een basis-emitterontwerp is = Vcc - VBE

De weerstanden gezien in de 4.17 zijn RB + RE , wat wordt weergegeven als (β + 1), en het resultaat is wat we hebben in vergelijking 4.17.

Collector-zenderlus

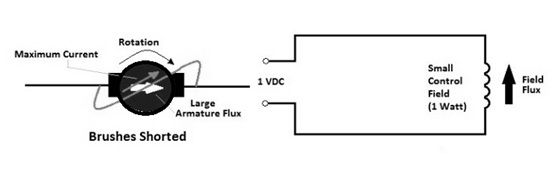

De bovenstaande afbeelding toont de collector-emitterlus, van toepassing De wet van Kirchhoff naar de aangegeven lus met de klok mee, krijgen we de volgende vergelijking:

GISTEREN + JE BENT + ICRC - VCC = 0

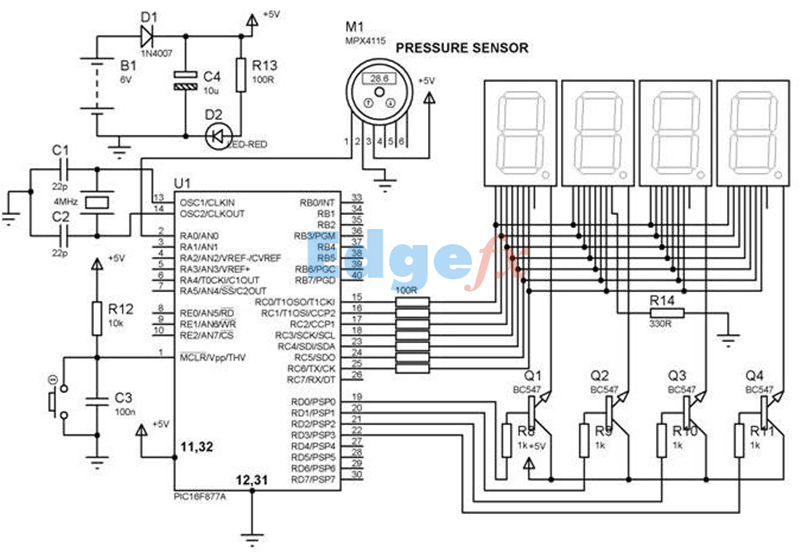

Een praktisch voorbeeld oplossen voor een emitter-gestabiliseerd bias-circuit zoals hieronder gegeven:

Evalueer het volgende voor het emitterbiasnetwerk zoals weergegeven in de bovenstaande afbeelding 4.22:

- IB

- IC

- JE BENT

- U

- EN

- ENZ

- VBC

Verzadigingsniveau bepalen

De maximale collectorstroom die de collector wordt verzadigingsniveau voor een emitter-bias-netwerk kan worden berekend door de identieke strategie toe te passen die eerder voor onze was toegepast vast voorspanning circuit

Het kan worden geïmplementeerd door een kortsluiting te creëren tussen de collector- en emitterkabels van de BJT, zoals aangegeven in het bovenstaande diagram 4.23, en dan kunnen we de resulterende collectorstroom evalueren met behulp van de volgende formule:

Voorbeeldprobleem voor het oplossen van verzadigingsstroom in een emitter-gestabiliseerd BJT-circuit:

Laadlijnanalyse

De load-line-analyse van het emitter-bias BJT-circuit lijkt veel op onze eerder besproken fixed-bias-configuratie.

Het enige verschil is dat het niveau van IB [zoals afgeleid in onze vergelijking (4.17)] het niveau van IB definieert op de kenmerken zoals getoond in de volgende figuur 4.24 (aangegeven als IBQ).

Vorige: Load-Line-analyse in BJT-circuits Vervolg: Voltage-Divider Bias in BJT-circuits - Meer stabiliteit zonder bètafactor