Het verhogen van de uitvoeringssnelheid van het programma verhoogt bijgevolg de snelheid van de processor. Er zijn veel manieren uitgevonden, zowel hardware-implementatie als softwarearchitectuur, om de uitvoeringssnelheid te verhogen. Opgemerkt werd dat door het gelijktijdig uitvoeren van instructies de tijd die nodig is voor de uitvoering kan worden verkort. Het concept van parallellisme in programmeren werd voorgesteld. Volgens dit kan meer dan één instructie per klokcyclus worden uitgevoerd. Dit concept kan door een programmeur worden geoefend door middel van verschillende technieken, zoals Pipelining, meerdere uitvoeringseenheden en meerdere kernen Van al deze parallellismemethoden wordt pipelining het meest toegepast. Dus hoe kan een instructie worden uitgevoerd in de pipelining-methode? Hoe verhoogt het de snelheid van uitvoering?

Wat is pijplijnen?

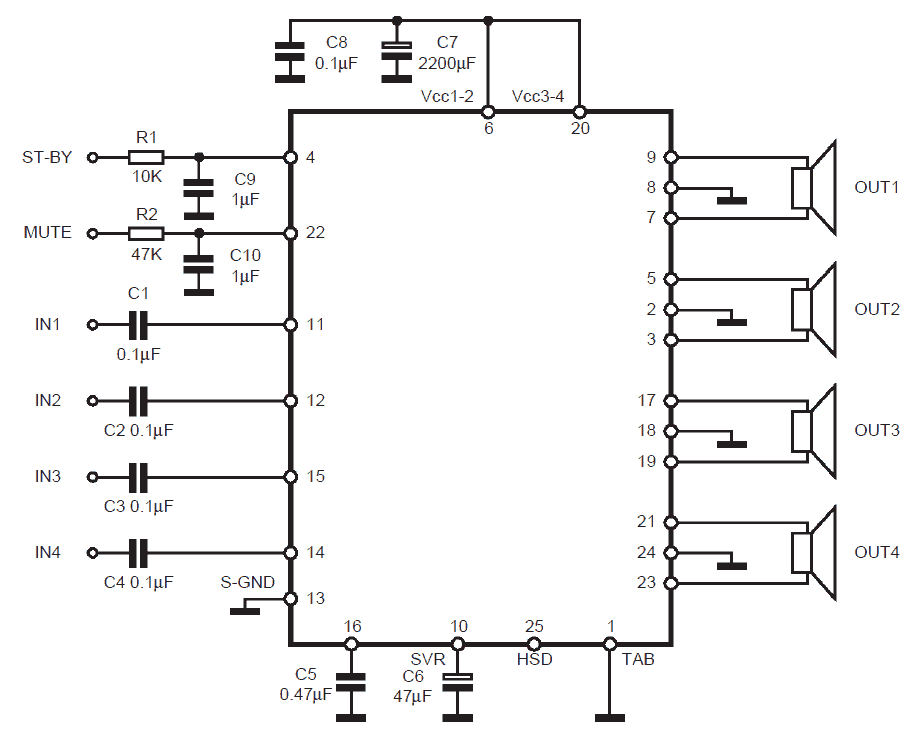

Laten we, om het concept van pipelining te begrijpen, kijken naar het basisniveau van hoe het programma wordt uitgevoerd. Instructie is het kleinste uitvoeringspakket van een programma. Elke instructie bevat een of meer bewerkingen. Eenvoudige scalaire processors voeren een of meer instructies per klokcyclus uit, waarbij elke instructie slechts één bewerking bevat. Instructies worden uitgevoerd als een opeenvolging van fasen om de verwachte resultaten te produceren. Deze volgorde wordt hieronder gegeven

Instructie Uitvoeringsvolgorde

- IF: haalt de instructie op in het instructieregister.

- ID: Instructiedecodering, decodeert de instructie voor de opcode.

- AG: Address Generator, genereert het adres.

- DF: Data Fetch, haalt de operanden op in het dataregister.

- EX: Execution, voert de gespecificeerde operatie uit.

- WB: Schrijf terug, schrijft het resultaat terug naar het register.

Niet alle instructies vereisen alle bovenstaande stappen, maar de meeste wel. Deze stappen gebruiken verschillende hardwarefuncties. Bij pipelining worden deze verschillende fasen gelijktijdig uitgevoerd. Bij pipelining worden deze fasen als onafhankelijk beschouwd tussen verschillende bewerkingen en kunnen ze elkaar overlappen. Zo kunnen meerdere bewerkingen tegelijkertijd worden uitgevoerd, waarbij elke bewerking zich in zijn eigen onafhankelijke fase bevindt.

Instructie Pipelining

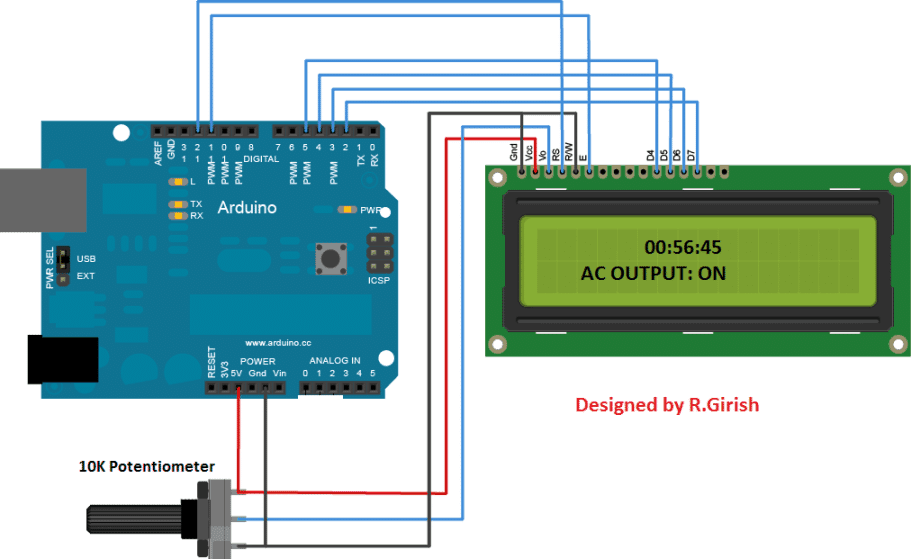

Laten we eens kijken hoe instructies worden verwerkt bij pipelining. Dit kan gemakkelijk worden begrepen door het onderstaande diagram.

Instructie Pipelining

Stel dat de instructies onafhankelijk zijn. In een eenvoudige pipelining-processor is er op een bepaald moment slechts één bewerking in elke fase. De beginfase is de IF-fase. Dus bij de eerste klokcyclus wordt één bewerking opgehaald. Wanneer de volgende klokpuls arriveert, gaat de eerste bewerking naar de ID-fase en laat de IF-fase leeg. Nu wordt deze lege fase toegewezen aan de volgende operatie. Dus tijdens de tweede klokpuls bevindt de eerste bewerking zich in de ID-fase en de tweede bewerking bevindt zich in de IF-fase.

Voor de derde cyclus bevindt de eerste bewerking zich in de AG-fase, de tweede bewerking bevindt zich in de ID-fase en de derde bewerking bevindt zich in de IF-fase. Op deze manier worden instructies gelijktijdig uitgevoerd en na zes cycli zal de processor een volledig uitgevoerde instructie per klokcyclus uitvoeren.

Is deze instructie opeenvolgend uitgevoerd, in eerste instantie moet de eerste instructie alle fasen doorlopen, dan wordt de volgende instructie opgehaald? Voor het uitvoeren van elke instructie heeft de processor dus zes klokcycli nodig. Maar in een pijplijnprocessor, aangezien de uitvoering van instructies gelijktijdig plaatsvindt, vereist alleen de initiële instructie zes cycli en worden alle resterende instructies als één per cyclus uitgevoerd, waardoor de uitvoeringstijd wordt verkort en de snelheid van de processor wordt verhoogd.

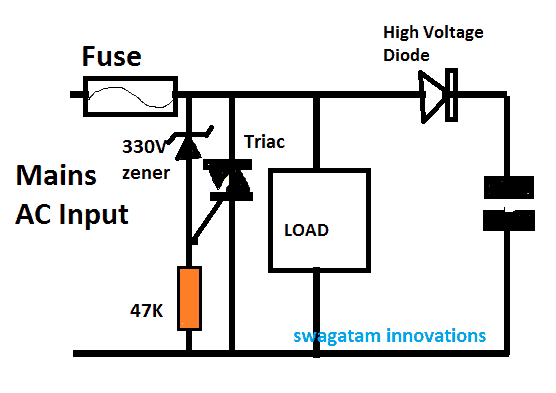

Pipelining Architectuur

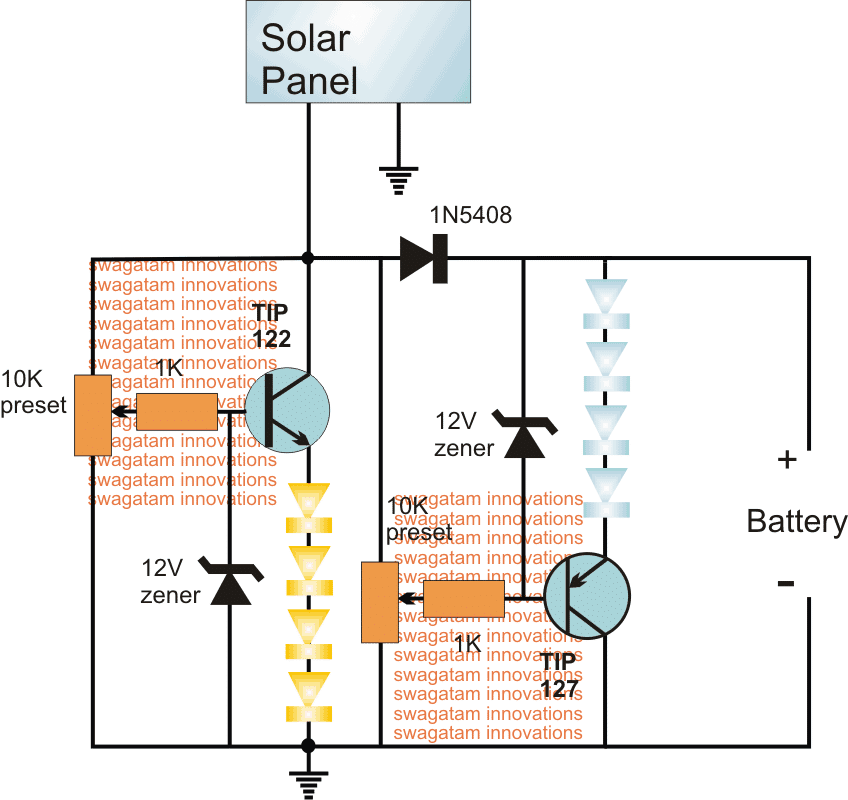

Parallellisme kan worden bereikt met hardware-, compiler- en softwaretechnieken. Om het concept van pipelining in te exploiteren computer architectuur veel processoreenheden zijn met elkaar verbonden en werken gelijktijdig. In de pijplijnprocessorarchitectuur zijn er afzonderlijke verwerkingseenheden voor gehele getallen en drijvende-komma-instructies. Terwijl in sequentiële architectuur een enkele functionele eenheid wordt geboden.

Processoreenheid met pijplijn

Bij statische pijplijnen moet de processor de instructie door alle fasen van de pijplijn doorgeven, ongeacht de instructie. In een dynamische pijplijnprocessor kan een instructie de fasen omzeilen, afhankelijk van de vereiste, maar moet deze in volgorde worden verplaatst. In een complexe dynamische pijplijnprocessor kan de instructie zowel de fasen omzeilen als de fasen buiten de juiste volgorde kiezen.

Pipelining in RISC-processors

Het meest populair RISC-architectuur ARM-processor volgt 3-traps en 5-traps pipelining. Bij 3-traps pipelining zijn de fasen: Fetch, Decode en Execute. Deze pipelining heeft een latentie van 3 cycli, aangezien een individuele instructie 3 klokcycli nodig heeft om te voltooien.

ARM 3-traps Pipelining

Voor een juiste implementatie van pipelining moet de hardware-architectuur ook worden geüpgraded. De hardware voor 3-traps pipelining omvat een registerbank, ALU, barrel shifter, adresgenerator, een incrementer, instructiedecoder en dataregisters.

ARM 3 Stage Pipelining Datapath

In 5 fasen pipelining zijn de fasen: Fetch, Decode, Execute, Buffer / data en Write back.

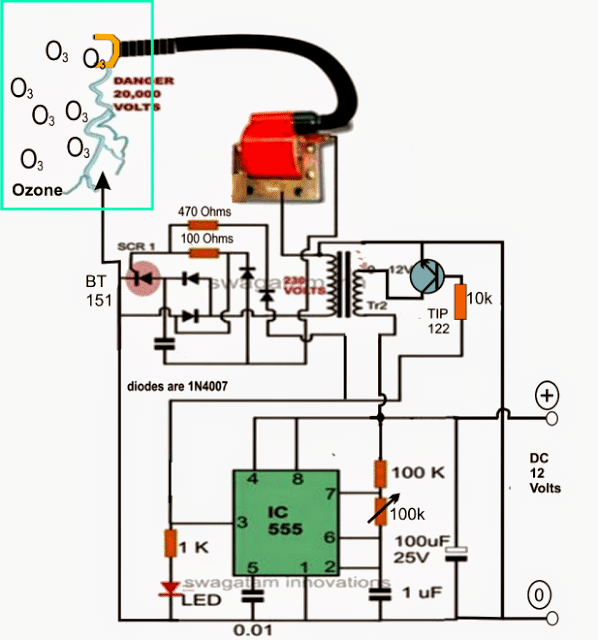

Gevaren voor pijpleidingen

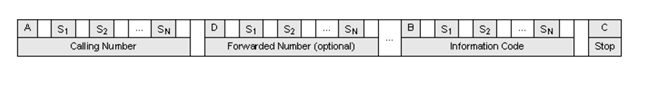

In een typisch computerprogramma zijn er naast eenvoudige instructies ook vertakkingsinstructies, onderbrekingsoperaties, lees- en schrijfinstructies. Pipelining is niet geschikt voor allerlei instructies. Wanneer sommige instructies worden uitgevoerd bij pijplijnen, kunnen ze de pijpleiding blokkeren of volledig doorspoelen. Dit soort problemen dat tijdens het pijplijnen wordt veroorzaakt, wordt Pipelining Hazards genoemd.

In de meeste computerprogramma's wordt het resultaat van de ene instructie gebruikt als een operand door de andere instructie. Wanneer dergelijke instructies in pijplijn worden uitgevoerd, treedt er een storing op omdat het resultaat van de eerste instructie niet beschikbaar is wanneer instructie twee begint met het verzamelen van operanden. Dus instructie twee moet stoppen totdat instructie één wordt uitgevoerd en het resultaat wordt gegenereerd. Dit type gevaar wordt Read-after-write pipelining-gevaar genoemd.

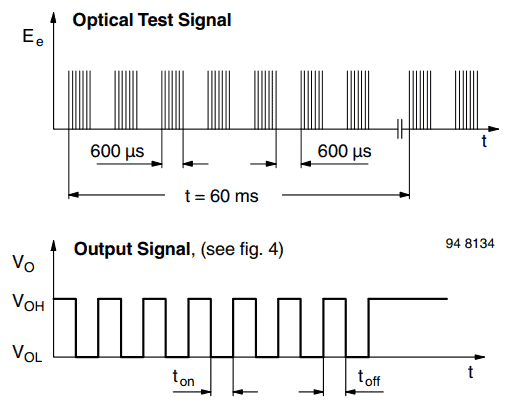

Lezen na schrijven Gevaar voor pipelining

Het uitvoeren van vertakkingsinstructies levert ook gevaar op voor het leggen van leidingen. Branch instructies tijdens uitvoering in pijpleidingen beïnvloedt de ophaalfasen van de volgende instructies.

Pijplijngedrag van takken

Voordelen van Pipelining

- De doorvoer van instructies neemt toe.

- Toename van het aantal pijplijnfasen verhoogt het aantal gelijktijdig uitgevoerde instructies.

- Snellere ALU kan worden ontworpen wanneer pijpleiding wordt gebruikt.

- Pijplijn CPU's werken op hogere klokfrequenties dan de RAM.

- Pipelining verhoogt de algehele prestaties van de CPU.

Nadelen van pijplijnen

- Het ontwerpen van de pijplijnprocessor is complex.

- De latentie van instructies neemt toe bij processors met pijplijn.

- De doorvoer van een pijplijnprocessor is moeilijk te voorspellen.

- Hoe langer de pijpleiding, hoe groter het gevaar voor instructies van filialen.

Pipelining profiteert van alle instructies die een vergelijkbare reeks stappen volgen voor uitvoering. Processors met complexe instructies waarbij elke instructie zich anders gedraagt dan de andere, zijn moeilijk te pipelineeren. Verwerkers hebben redelijke werktuigen met 3 of 5 fasen van de pijpleiding, omdat naarmate de pijplijndiepte toeneemt, de daarmee verband houdende gevaren toenemen. Noem enkele van de pijplijnprocessors met hun pijplijnfase?