Instructieset of instructiesetarchitectuur is de structuur van de computer die de computer opdrachten geeft om de computer te begeleiden bij het verwerken van gegevensmanipulatie. Instructieset bestaat uit instructies, adresseringsmodi, native gegevenstypen, registers, interrupt, afhandeling van uitzonderingen en geheugenarchitectuur. De instructieset kan in software worden geëmuleerd met behulp van een tolk of kan worden ingebouwd in de hardware van de processor. De architectuur van de instructieset kan worden beschouwd als een grens tussen software en hardware. Classificatie van microcontrollers en microprocessors kunnen worden gedaan op basis van de RISC- en CISC-instructiesetarchitectuur.

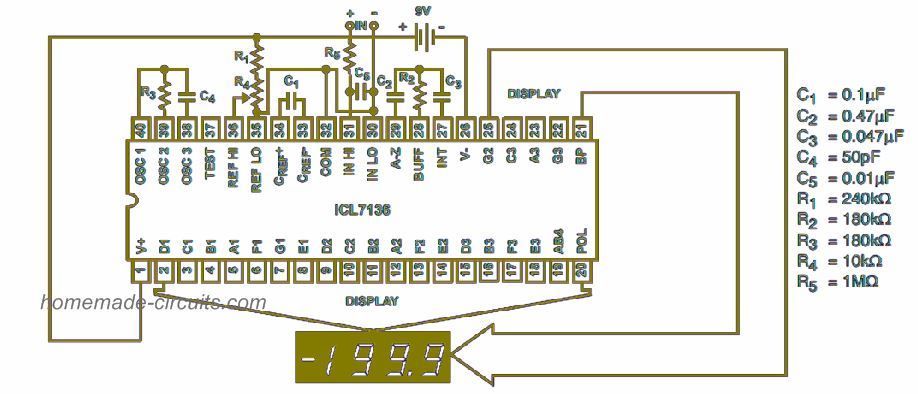

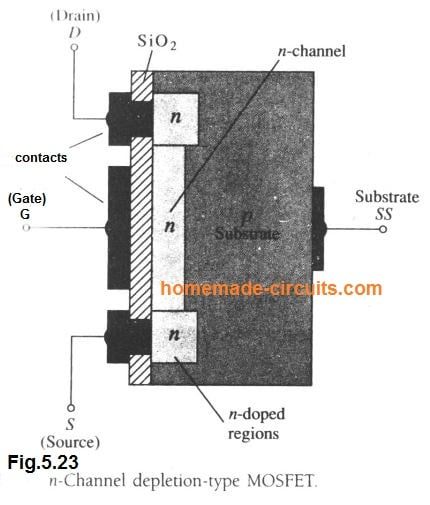

Instructieset van Processor

De instructieset specificeert de processorfunctionaliteit, inclusief de bewerkingen die worden ondersteund door de processor, opslagmechanismen van de processor en de manier waarop de programma's voor de processor worden gecompileerd.

Wat is RISC en CISC?

De RISC en CISC kan als volgt worden uitgebreid:

RISC vertegenwoordigt de Computer met gereduceerde instructieset en

CISC vertegenwoordigt de computer met complexe instructieset.

RISC-architectuur (Reduced Instruction Set Computer)

RISC-architectuur

De microcontroller-architectuur die een kleine en sterk geoptimaliseerde set instructies gebruikt, wordt de Reduced Instruction Set Computer genoemd of eenvoudigweg RISC genoemd. Het wordt ook wel LOAD / STORE-architectuur genoemd.

Eind jaren zeventig en begin jaren tachtig werden RISC-projecten voornamelijk ontwikkeld vanuit Stanford, UC-Berkley en IBM. Het John Coke van IBM-onderzoeksteam ontwikkelde RISC door het aantal instructies dat nodig is om berekeningen sneller te verwerken dan de CISC, te verminderen. De RISC-architectuur is sneller en de chips die nodig zijn voor de fabricage van de RISC-architectuur zijn ook goedkoper in vergelijking met de CISC-architectuur.

Typische kenmerken van RISC-architectuur

- Pipelining-techniek van RISC, voert meerdere delen of stadia van instructies tegelijkertijd uit zodat elke instructie op de CPU wordt geoptimaliseerd. Daarom hebben de RISC-processors Clock per Instruction van één cyclus, en dit wordt One Cycle Execution genoemd.

- Het optimaliseert de gebruik van register met meer registers in het RISC en meer interacties binnen het geheugen kunnen worden voorkomen.

- Eenvoudige adresseringsmodi, zelfs complexe adressering kan worden gedaan door rekenkundige bewerkingen te gebruiken EN / OF logische bewerkingen

- Het vereenvoudigt het compilerontwerp door identieke registers voor algemene doeleinden te gebruiken, waardoor elk register in elke context kan worden gebruikt.

- Voor een efficiënt gebruik van de registers en optimalisatie van het gebruik van pipelining is een gereduceerde instructieset vereist.

- Het aantal bits dat voor de opcode wordt gebruikt, wordt verminderd.

- Over het algemeen zijn er 32 of meer registers in het RISC.

Voordelen van RISC-processorarchitectuur

- Vanwege de kleine set instructies van RISC kunnen taalcompilers op hoog niveau efficiëntere code produceren.

- RISC biedt vrijheid om de ruimte op microprocessoren vanwege zijn eenvoud.

- In plaats van Stack te gebruiken, gebruiken veel RISC-processors de registers om argumenten door te geven en de lokale variabelen vast te houden.

- RISC-functies gebruiken slechts een paar parameters en de RISC-processors kunnen de aanroepinstructies niet gebruiken en gebruiken daarom instructies met een vaste lengte die gemakkelijk te pijplijnen zijn.

- De snelheid van de bewerking kan worden gemaximaliseerd en de uitvoeringstijd kan worden geminimaliseerd.

- Er zijn heel weinig instructieformaten (minder dan vier), een paar instructies (ongeveer 150) en een paar adresseringsmodi (minder dan vier) nodig.

Nadelen van de RISC-processorarchitectuur

- Met de toename in lengte van de instructies, neemt de complexiteit toe voor de RISC-processors om uit te voeren vanwege de karaktercyclus per instructie.

- De prestaties van de RISC-processors hangen grotendeels af van de compiler of programmeur, aangezien de kennis van de compiler een grote rol speelt bij het converteren van de CISC-code naar een RISC-code, vandaar dat de kwaliteit van de gegenereerde code afhankelijk is van de compiler.

- Bij het herschikken van de CISC-code naar een RISC-code, ook wel code-uitbreiding genoemd, zal de omvang toenemen. En de kwaliteit van deze code-uitbreiding hangt weer af van de compiler, en ook van de instructieset van de machine.

- De first level cache van de RISC-processors is ook een nadeel van de RISC, waarin deze processors grote geheugencaches op de chip zelf hebben. Voor het voeren van de instructies hebben ze heel veel nodig snelle geheugensystemen

CISC-architectuur (Complex Instruction Set Computer)

De belangrijkste bedoeling van de CISC-processorarchitectuur is om de taak te voltooien door minder assemblagelijnen te gebruiken. Voor dit doel is de processor gebouwd om een reeks bewerkingen uit te voeren. Complexe instructie wordt ook wel MULT genoemd, dat werkt geheugenbanken van een computer rechtstreeks zonder dat de compiler opslag- en laadfuncties uitvoert.

CISC-architectuur

Kenmerken van CISC-architectuur

- Om de computerarchitectuur te vereenvoudigen, ondersteunt CISC microprogrammering.

- CISC heeft een groter aantal voorgedefinieerde instructies waardoor talen op hoog niveau eenvoudig te ontwerpen en implementeren zijn.

- CISC bestaat uit minder registers en meer adresseermodi, doorgaans 5 tot 20.

- CISC-processor heeft verschillende cyclustijden nodig voor het uitvoeren van instructies - cycli met meerdere klokken.

- Vanwege de complexe instructieset van de CISC is de pipelining-techniek erg moeilijk.

- CISC bestaat uit een groter aantal instructies, doorgaans van 100 tot 250.

- Speciale instructies worden zeer zelden gebruikt.

- Operanden in het geheugen worden gemanipuleerd door instructies.

Voordelen van CISC-architectuur

- Elke machinetaalinstructie wordt gegroepeerd in een microcode-instructie en dienovereenkomstig uitgevoerd, en vervolgens ingebouwd opgeslagen in het geheugen van de hoofdprocessor, genaamd microcode-implementatie.

- Aangezien het microcode-geheugen sneller is dan het hoofdgeheugen, kan de microcode-instructieset worden geïmplementeerd zonder aanzienlijke snelheidsvermindering ten opzichte van een vast bedrade implementatie.

- De volledige nieuwe instructieset kan worden afgehandeld door het ontwerp van het microprogramma te wijzigen.

- CISC, het aantal instructies dat nodig is om een programma te implementeren, kan worden verminderd door rijke instructiesets te bouwen en kan ook worden gemaakt om het trage hoofdgeheugen efficiënter te gebruiken.

- Door de superset aan instructies die uit alle eerdere instructies bestaat, is microcodering hierdoor eenvoudig.

Nadelen van CISC

- De hoeveelheid kloktijd die door verschillende instructies wordt ingenomen, zal - hierdoor - de prestaties van de machine vertragen.

- De complexiteit van de instructieset en de chiphardware nemen toe naarmate elke nieuwe versie van de processor uit een subset van eerdere generaties bestaat.

- Slechts 20% van de bestaande instructies wordt gebruikt in een typisch programmeergebeurtenis, hoewel er veel gespecialiseerde instructies bestaan die niet eens vaak worden gebruikt.

- De voorwaardelijke codes worden ingesteld door de CISC-instructies als een neveneffect van elke instructie die tijd kost voor deze instelling - en, aangezien de daaropvolgende instructie de conditiecodebits verandert - dus, moet de compiler de conditiecodebits onderzoeken voordat dit gebeurt.

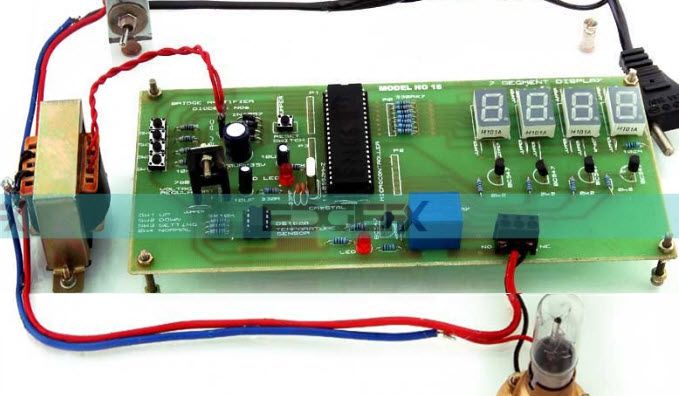

RISC Vs. CISC

- De verspillingscycli kunnen door de programmeur worden voorkomen door de onnodige code in de RISC te verwijderen, maar tijdens het gebruik van de CISC-code leidt dit tot verspilling van cycli vanwege de inefficiëntie van de CISC.

- In RISC is elke instructie bedoeld om een kleine taak uit te voeren, zodat, om een complexe taak uit te voeren, meerdere kleine instructies samen worden gebruikt, terwijl er maar een paar instructies nodig zijn om dezelfde taak uit te voeren met CISC - omdat het in staat is om complexe taken uit te voeren aangezien de instructies vergelijkbaar zijn met een code in hoge talen.

- CISC wordt meestal gebruikt voor computers, terwijl RISC wordt gebruikt voor smartphones, tablets en andere elektronische apparaten.

De volgende afbeelding laat meer verschillen zien tussen RISC en CISC

RISC Vs. CISC

Daarom bespreekt dit artikel de kenmerken van de RISC- en CISC-architecturen van de RISC- en CISC-processorsarchitectuur de voordelen en nadelen van RISC en CISC, en de verschillen tussen de RISC- en CISC-architecturen met een kort idee. Voor meer informatie over de RISC- en CISC-architecturen kunt u uw vragen stellen door hieronder te reageren.

Fotocredits:

- Instructieset van Processor door arstechnica

- RISC Architecture door lsi-wedstrijd

- RISC vs. CISC door csarassignment