Twee hoofdtypen FET's die momenteel bestaan, zijn: JFET's en MOSFET's.

MOSFET's kunnen verder worden ingedeeld in uitputtingstype en verbeteringstype. Beide typen definiëren de fundamentele werkingsmodus van MOSFET's, terwijl de term MOSFET zelf de afkorting is van metaaloxide-halfgeleider-veldeffecttransistor.

Omdat de twee typen verschillende werkeigenschappen hebben, zullen we ze elk afzonderlijk in verschillende artikelen evalueren.

Verschil tussen Enhancement and Depletion MOSFET

Kortom, in tegenstelling tot enhancement MOSFET's, bevinden depletion MOSFET's zich in een aan-toestand, zelfs in de aanwezigheid van een 0 V over de gate-to-source terminals (VGS).

Voor een enhancement-MOSFET moet de gate-to-source-spanning (VGS) hoger zijn dan de gate-to-source-drempelspanning (VGS (th)) om het te laten geleiden

Voor een N-kanaal uitputtings-MOSFET is de VGS (th) -waarde echter hoger dan 0 V. Dit betekent dat zelfs als VGS = 0 V, een uitputtings-MOSFET stroom kan geleiden. Om het uit te schakelen, moet de VGS van een uitputtings-MOSFET worden verlaagd tot onder de VGS (th) (negatief).

In dit huidige artikel bespreken we de uitputtingstype MOSFET, waarvan wordt gezegd dat ze kenmerken hebben die overeenkomen met die van een JFET. De overeenkomst is tussen afsnijding en verzadiging nabij IDSS.

Basisconstructie

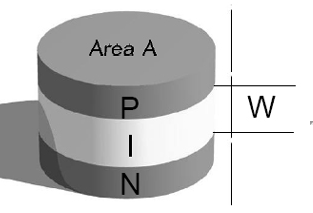

Figuur 5.23 toont de interne basisstructuur van een n-kanaals uitputtingstype MOSFET.

We kunnen een blok p-type materiaal vinden dat is gemaakt met behulp van een siliconenbasis. Dit blok wordt het substraat genoemd.

Het substraat is de basis of de fundering waarover een MOSFET wordt gebouwd. Voor sommige MOSFET's is het intern verbonden met de 'source'-terminal. Ook bieden veel apparaten een extra output in de vorm van SS, met een 4-terminal MOSFET, zoals onthuld in figuur 5.23

De drain en de source-aansluitingen zijn via geleidende contacten verbonden met n-gedoteerde locaties en bevestigd via een n-kanaal, zoals aangegeven in dezelfde afbeelding.

De poort is ook verbonden met een metalen laag, hoewel deze is geïsoleerd van het n-kanaal door een fijne laag siliciumdioxide (SiOtwee

SiOtweebezit een unieke vorm van isolatie-eigenschap, diëlektricum genaamd, dat een tegengesteld elektrisch veld in zichzelf creëert als reactie op een extern aangelegd elektrisch veld.

Omdat het een isolerende laag is, is het materiaal SiOtweebiedt ons de volgende belangrijke informatie:

Met dit materiaal wordt een volledige isolatie ontwikkeld tussen de gate-terminal en het mosfet-kanaal.

Bovendien komt het door SiOtwee, kan de poort van de mosfet een extreem hoge ingangsimpedantie hebben.

Vanwege deze vitale eigenschap van hoge ingangsimpedantie, kan de poortstroom IGis vrijwel nul ampère voor elke DC-vooringenomen MOSFET-configuratie.

Basisbediening en kenmerken

AS is te zien in figuur 5.24, de gate-to-source-spanning is geconfigureerd op nul volt door de twee terminals met elkaar te verbinden, terwijl een spanning VDSwordt toegepast over de afvoer- en bronterminals.

Met de bovenstaande instelling zorgt de afvoerzijde voor een positief potentiaal door de n-kanaals vrije elektronen, samen met een gelijkwaardige stroom door het JFET-kanaal. Ook de resulterende huidige VGS= 0V wordt nog steeds geïdentificeerd als IDSS, zoals weergegeven in Fig.5.25

We kunnen zien dat in figuur 5.26 de poortbronspanning VGSkrijgt een negatief potentiaal in de vorm van -1V.

Deze negatieve potentiaal probeert elektronen naar het p-kanaalsubstraat te dwingen (aangezien ladingen afstoten), en gaten uit het p-kanaalsubstraat te trekken (aangezien tegengestelde ladingen aantrekken).

Afhankelijk van hoe groot deze negatieve bias VGSDat wil zeggen, een recombinatie van gaten en elektronen vindt plaats wat resulteert in de reductie van vrije elektronen in het n-kanaal dat beschikbaar is voor de geleiding. Hogere niveaus van negatieve bias resulteren in een hogere mate van recombinatie.

De afvoerstroom wordt dientengevolge verminderd naarmate de bovenstaande negatieve voorspanningstoestand toeneemt, wat wordt bewezen in figuur 5.25 voor V.GSniveaus van VGS= -1, -2 enzovoort, tot het afknijpmerkteken van -6V.

De afvoerstroom als resultaat verloopt samen met de overdrachtscurve-plot net als die van a JFET.

Nu, voor de positieve VGSwaarden trekt de poortpositief overtollige elektronen (vrije dragers) aan van het p-type substraat vanwege de omgekeerde lekstroom. Dit zal nieuwe dragers vormen door de resulterende botsingen over de versnellende deeltjes.

Omdat de gate-to-source-spanning de neiging heeft om met de positieve snelheid te stijgen, vertoont de afvoerstroom een snelle toename, zoals bewezen in figuur 5.25 om dezelfde redenen als hierboven besproken.

De opening tussen de curven van VGS= 0V en VGS= +1 geeft duidelijk de hoeveelheid weer waarmee de stroom is toegenomen als gevolg van de 1 - V-variatie van de VGS

Vanwege de snelle stijging van de afvoerstroom moeten we voorzichtig zijn met de maximale stroomsterkte, anders kan deze de positieve gate-spanningslimiet overschrijden.

Bijvoorbeeld, voor het apparaattype dat is afgebeeld in figuur 5.25, wordt een V toegepastGS= + 4V zou ervoor zorgen dat de afvoerstroom stijgt tot 22,2 mA, wat de maximale doorslaggrens (stroom) van het apparaat kan overschrijden.

De bovenstaande voorwaarde laat zien dat het gebruik van een positieve gate-to-source-spanning een groter effect heeft op de hoeveelheid vrije dragers in het kanaal, in tegenstelling tot wanneer VGS= 0V.

Dit is de reden waarom het positieve poortspanningsgebied op de afvoer- of overdrachtskarakteristieken algemeen bekend staat als verbeteringsgebied Dit gebied ligt tussen de cut-off en het saturatieniveau van IDSSof het uitputtingsgebied.

Een voorbeeldprobleem oplossen

Voordelen en toepassingen

In tegenstelling tot MOSFET's in de enhancement-modus, waar we de afvoerstroom tot nul zien dalen als reactie op een nul-gate-to-source-spanning, heeft de moderne uitputtingsmodus-FET een merkbare stroom met een nul-gate-spanning. Om precies te zijn, de drain-to-source-weerstand is meestal 100 ohm bij nulspanning.

Zoals aangegeven in de bovenstaande grafiek, is de ON-weerstand rds(Aan)vs analoog signaalbereik ziet eruit als een praktisch vlakke respons. Dit kenmerk, in combinatie met de lage capaciteitsniveaus van deze geavanceerde uitputtingstypes, maakt het mogelijk dat ze specifiek ideaal zijn als analoge schakelaars voor audio- en videoschakeltoepassingen.

Het 'normal-on'-attribuut van de uitputtingsmodus MOSFET maakt het mogelijk dat het apparaat perfect geschikt is voor enkele FET-stroomregelaars.

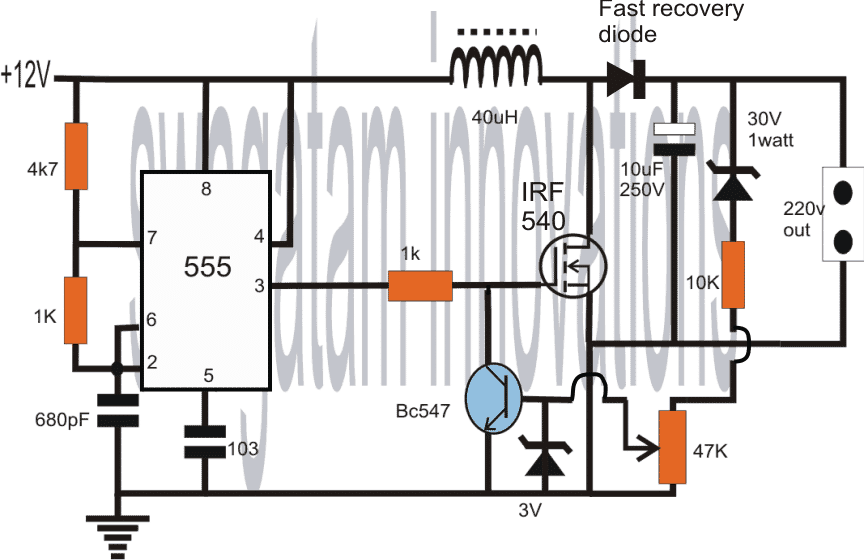

Een voorbeeld van zo'n circuit is te zien in de volgende afbeelding.

De Rs-waarde kan worden bepaald met behulp van de formule:

Rs= VGSuit[1 - (ID/IKDSS1/2] / ID

waar ikD is de hoeveelheid geregelde stroom die nodig is aan de uitgang.

Het belangrijkste voordeel van uitputtingsmodus MOSFET's in stroombrontoepassingen is hun minimale afvoercapaciteit, waardoor ze geschikt zijn voor voorspanningstoepassingen in circuits met lage ingangslekkage en gemiddelde snelheid (> 50 V / us).

De onderstaande afbeelding toont een front-end met lage lekstroom met een dubbele lage lekstroomfunctie FET.

Over het algemeen zal aan beide zijden van de JFET een vooringenomenheid zijn bij ID = 500 uA. Daarom wordt de stroom die kan worden verkregen voor laadcompensatie en strooicapaciteit beperkt tot 2ID of, in dergelijke gevallen, 1,0 mA. De overeenkomstige functies van de JFET zijn in de productie bewezen en staan op de datasheet vermeld.

Cs symboliseert de uitgangscapaciteit van de 'staart'-stroombron van de ingangstrap. Deze capaciteit is cruciaal in niet-inverterende versterkers, vanwege het feit dat de ingangstrap aanzienlijke signaaluitwisselingen door dit netwerk ervaart, en de laadstromen in Cs kunnen groot zijn. In het geval dat normale stroombronnen worden gebruikt, kan deze staartcapaciteit verantwoordelijk zijn voor een merkbare verslechtering van de slew-rate in niet-inverterende circuits (vergeleken met inverterende toepassingen, waar de laadstromen in Cs minimaal zijn).

De daling van de slew-rate kan worden uitgedrukt als:

1/1+ (Cs / Sc)

Zolang Cs lager is dan Cc (de compensatiecondensator), kan er nauwelijks variatie in de slew rate zijn. Werkend met de DMOS FET, kan Cs ongeveer 2 pF zijn. Deze strategie zorgt voor een enorme verbetering van de slew-rate. Waar stroomtekorten van meer dan 1 tot 5 mA nodig zijn, kan het apparaat worden voorgespannen in de verbeteringsmodus om maar liefst 20 mA te genereren voor een maximale VGS van +2,5 V, waarbij een minimale uitgangscapaciteit een belangrijk aspect blijft.

De volgende toepassing hieronder vertoont een juist stroombroncircuit in verbeteringsmodus.

Een 'normaal aan'-analoge schakelaar zou kunnen worden gebouwd voor vereisten waarbij standaardcondities nodig worden tijdens een stroomstoring, bijvoorbeeld bij het automatisch opzoeken van testinstrumenten of om te zorgen voor een nauwkeurige start van logische circuits bij het inschakelen.

De verlaagde negatieve drempelspanning van het apparaat biedt basisvoorwaarden voor de aandrijving en maakt werken met minimale spanning mogelijk.

De onderstaande schakeling toont de gemeenschappelijke bias-factoren voor elke analoge DMOS-schakelaar met uitputtingmodus.

Om het apparaat uit te schakelen, is een negatieve spanning nodig op de poort. Dat gezegd hebbende, zou de inschakelweerstand kunnen worden geminimaliseerd wanneer de FET bovendien wordt verbeterd met behulp van een positieve poortspanning, waardoor deze specifiek in het enhancement-mode-gebied samen met het depletion-mode-gebied mogelijk is.

Dit antwoord is te zien in de volgende grafiek.

De hoogfrequente versterking van de eenheid, samen met zijn lage capaciteitswaarden, levert een verhoogde 'figure of merit' op. Het is echt een cruciaal element in VHF- en UHF-versterking, dat het gain-bandwidth-product (GBW) van de FET specificeert, dat kan worden weergegeven als:

GBW = gfs / 2 Pi (Cin+ Cuit

MOSFET van het p-Channel Depletion-Type

De constructie van een MOSFET van het p-kanaal uitputtingstype is een perfecte omkering van een n-kanaalversie die wordt getoond in figuur 5.23. Dit betekent dat het substraat nu de vorm aanneemt van een n-type en het kanaal een p-type wordt, zoals te zien is in figuur 5.28a hieronder.

De klemidentificatie blijft ongewijzigd, maar de spanning en de stroompolariteiten zijn omgekeerd, zoals aangegeven in dezelfde afbeelding. De afvoerkarakteristieken zouden precies zijn zoals afgebeeld in figuur 5.25, behalve VDSteken dat in dit geval een negatieve waarde krijgt.

De afvoerstroom IDvertoont in dit geval ook een positieve polariteit, dat komt omdat we de richting al hebben omgekeerd. VGStoont een tegengestelde polariteit, wat begrijpelijk is, zoals aangegeven in figuur 5.28c.

Omdat VGSis omgekeerd produceert een spiegelbeeld voor de overdrachtskarakteristieken zoals aangegeven in figuur 5,28b.

Dit betekent dat de afvoerstroom toeneemt in de positieve VGSregio vanaf het afkappunt bij VGS= Vp tot ikDSS, dan blijft het stijgen als de negatieve waarde van VGSstijgt.

Symbolen

De grafische tekens voor een MOSFET van het n- en p-kanaal depletie-type zijn te zien in de bovenstaande figuur 5.29.

Bekijk de manier waarop de geselecteerde symbolen de ware structuur van het apparaat weergeven.

De afwezigheid van een directe verbinding (vanwege de poortisolatie) tussen de poort en het kanaal wordt gesymboliseerd door een opening tussen de poort en de verschillende aansluitingen van het symbool.

De verticale lijn die het kanaal vertegenwoordigt, is bevestigd tussen de afvoer en de bron en wordt 'vastgehouden' door het substraat.

In de bovenstaande afbeelding zijn voor elk type kanaal twee groepen symbolen weergegeven om te benadrukken dat bij sommige apparaten het substraat extern toegankelijk kan zijn, terwijl dit bij andere niet zichtbaar is.

MOSFET (Enhancement-Type)

Hoewel uitputtingstype en verbeteringstype MOSFET's er hetzelfde uitzien met hun interne structuren en functionele modus, kunnen hun kenmerken behoorlijk verschillen.

Het belangrijkste verschil is de afvoerstroom die afhangt van een specifiek niveau van gate-to-source-spanning voor de afsnijactie.

Juist, een n-kanaals MOSFET van het enhancement-type kan werken met een positieve gate / source-spanning, in plaats van een reeks negatieve potentialen die normaal een uitputtingstype MOSFET kunnen beïnvloeden.

Basisconstructie

U kunt de n-channel enhancement-type MOSFET in het volgende visualiseren

Afb.5.31.

Een materiaalsectie van het p-type wordt gecreëerd door middel van een siliciumbasis en wordt, zoals eerder geleerd, het substraat genoemd.

Dit substraat is in sommige gevallen intern verbonden met de bronpin in een uitputtingstype MOSFET, terwijl het in sommige gevallen is afgesloten als een vierde leiding om een externe regeling van het potentiaalniveau mogelijk te maken.

De source- en drainaansluitingen zijn zoals gewoonlijk verbonden met behulp van metalen contacten met n-gedoteerde gebieden.

Het kan echter belangrijk zijn om te visualiseren dat in Fig. 5.31 het kanaal tussen de twee n-gedoteerde gebieden ontbreekt.

Dit kan worden beschouwd als de fundamentele ongelijkheid tussen de interne lay-out van een uitputtingstype en een verbeteringstype MOSFET, dat wil zeggen de afwezigheid van een inherent kanaal dat een deel van het apparaat zou moeten zijn.

De SiO2-laag is nog steeds aanwezig, wat zorgt voor een isolatie tussen de metalen basis van de poortaansluiting en het gebied tussen de afvoer en de bron. Hier kan het echter worden gezien terwijl het gescheiden staat van het p-type materiaalgedeelte.

Uit de bovenstaande bespreking kunnen we concluderen dat een interne lay-out van depletion and enhancement MOSFET enkele overeenkomsten kan hebben, behalve het ontbrekende kanaal tussen drain / source voor een enhancement-type MOSFET.

Basisbediening en kenmerken

Voor een verbeteringstype MOSFET wanneer een 0 V wordt geïntroduceerd op zijn VGS, veroorzaakt het ontbrekende n-kanaal (waarvan bekend is dat het veel vrije draaggolven draagt) een stroomuitgang die nul is, wat heel anders is dan een uitputtingstype van MOSFET, met ID = IDSS.

In een dergelijke situatie kunnen grote hoeveelheden dragers in de vorm van elektronen vanwege een ontbrekend pad over drain / source-aansluitingen zich niet ophopen bij drain / source (vanwege de n-gedoteerde gebieden).

Door een positief potentieel toe te passen op VDS, met VGS ingesteld op nul volt en de SS-aansluiting kortgesloten met de source-aansluiting, vinden we eigenlijk een aantal in omgekeerde richting voorgespannen pn-overgangen tussen de n-gedoteerde gebieden en het p-substraat om enige opmerkelijke geleiding over afvoer naar de bron.

In Fig. 5.32 toont een toestand waarin VDS en VGS worden aangelegd met een positieve spanning hoger dan 0 V, waardoor de drain en gate op een positieve potentiaal staan ten opzichte van de source.

De positieve potentiaal bij de poort duwt de gaten in het p-substraat langs de rand van de SiO2-laag en verlaat de locatie en gaat dieper in de gebieden van het p-substraat, zoals weergegeven in de bovenstaande figuur. Dit gebeurt vanwege soortgelijke ladingen die elkaar afstoten.

Dit resulteert in een uitputtingsgebied dat dicht bij de SiO2-isolatielaag wordt gecreëerd zonder gaten.

Desondanks worden de p-substraatelektronen die de minderheidsdragers van het materiaal zijn naar de positieve poort getrokken en beginnen ze zich te verzamelen in het gebied dicht bij het oppervlak van de Si02-laag.

Vanwege de isolatie-eigenschappen van de SiO2-laag zorgen negatieve dragers ervoor dat de negatieve dragers niet worden geabsorbeerd bij de poortterminal.

Naarmate we het niveau van VGS verhogen, neemt ook de elektronendichtheid dicht bij het SiO2-oppervlak toe, totdat uiteindelijk het geïnduceerde n-type gebied een kwantificeerbare geleiding over de afvoer / bron mogelijk maakt.

De VGS-grootte die een optimale toename van de afvoerstroom veroorzaakt, wordt de drempelspanning genoemd, aangeduid door het symbool VT In datasheets kun je dit zien als VGS (Th).

Zoals hierboven geleerd, staat dit type MOSFET bekend als MOSFET's van het enhancement-type, vanwege de afwezigheid van een kanaal op VGS = 0 en 'verbeterd' met de positieve gate-to-source-spanningstoepassing.

U zult zien dat zowel depletie- als enhancement-type MOSFET's enhancement-type regio's vertonen, maar de term verbetering wordt gebruikt voor het laatste omdat het specifiek werkt met behulp van een verbeteringsmodus.

Wanneer VGS nu over de drempelwaarde wordt geduwd, zal de concentratie van de vrije dragers toenemen in het kanaal waar het wordt geïnduceerd. Hierdoor neemt de afvoerstroom toe.

Aan de andere kant, als we de VGS constant houden en het VDS-niveau (drain-to-source voltage) verhogen, zal dit er uiteindelijk voor zorgen dat de MOSFET zijn verzadigingspunt bereikt, zoals normaal ook zou gebeuren met elke JFET of een uitputting MOSFET.

Zoals getoond in Fig. 5.33 wordt de afvoerstroom ID afgevlakt met behulp van een afknijpproces, aangegeven door het smallere kanaal naar het afvoeruiteinde van het geïnduceerde kanaal.

Door de spanningswet van Kirchhoff toe te passen op de klemspanningen van de MOSFET in figuur 5.33, krijgen we:

Als VGS constant wordt gehouden op een specifieke waarde, bijvoorbeeld 8 V, en VDS wordt verhoogd van 2 naar 5 V, wordt de spanning VDG door Eq. 5.11 kon worden gezien als een daling van -6 naar -3 V, en het poortpotentiaal werd steeds minder positief ten opzichte van de afvoerspanning.

Deze reactie verhindert dat de vrije dragers of elektronen naar dit gebied van het geïnduceerde kanaal worden getrokken, wat op zijn beurt resulteert in een daling van de effectieve breedte van het kanaal.

Uiteindelijk neemt de kanaalbreedte af tot het punt van afknijpen, waardoor een verzadigingstoestand wordt bereikt die vergelijkbaar is met wat we al hebben geleerd in ons eerdere MOSFET-artikel over depletie.

Dit betekent dat het verder verhogen van de VDS met een vaste VGS geen invloed heeft op het saturatieniveau van ID, tot het punt waarop een storing wordt bereikt.

Als we naar figuur 5.34 kijken, kunnen we vaststellen dat voor een MOSFET zoals in figuur 5.33 met VGS = 8 V, verzadiging plaatsvindt op een VDS-niveau van 6 V. Om precies te zijn, wordt het VDS-verzadigingsniveau geassocieerd met het toegepaste VGS-niveau door:

Het impliceert dus ongetwijfeld dat wanneer de VT-waarde vast is, het verhogen van het niveau van VGS proportioneel hogere verzadigingsniveaus voor VDS zal veroorzaken door de locus van verzadigingsniveaus.

Verwijzend naar de kenmerken die in de bovenstaande afbeelding worden getoond, is het VT-niveau 2 V, wat duidelijk wordt door het feit dat de afvoerstroom is gedaald tot 0 mA.

Daarom kunnen we meestal zeggen:

Wanneer VGS-waarden lager zijn dan het drempelniveau voor MOSFET van het enhancement-type, is de afvoerstroom 0 mA.

We kunnen ook duidelijk zien in de bovenstaande figuur dat zolang de VGS hoger wordt verhoogd van VT naar 8 V, het overeenkomstige verzadigingsniveau voor ID ook toeneemt van 0 naar 10 mA-niveau.

Bovendien kunnen we verder opmerken dat de ruimte tussen de VGS-niveaus toeneemt met een toename van de waarde van VGS, waardoor de afvoerstroom oneindig stijgt.

We vinden dat de afvoerstroomwaarde gerelateerd is aan de gate-to-source-spanning voor VGS-niveaus die groter is dan VT, via de volgende niet-lineaire relatie:

De term die in een vierkante haak wordt weergegeven, is de term die verantwoordelijk is voor de niet-lineaire relatie tussen ID en VGS.

De term k is een constante en is een functie van de MOSFET-layout.

We kunnen de waarde van deze constante k achterhalen door de volgende vergelijking:

waarbij de ID (aan) en VGD (aan) elk waarden zijn die specifiek afhankelijk zijn van het kenmerk van het apparaat.

In de volgende Fig. 5.35 hieronder zien we dat de drain- en transfer-eigenschappen naast elkaar zijn gerangschikt om het transferproces over elkaar heen te verduidelijken.

In principe is het vergelijkbaar met het proces dat eerder is uitgelegd voor JFET en MOSFET's van het uitputtingstype.

In dit geval moeten we echter onthouden dat de afvoerstroom 0 mA is voor VGS VT.

Hier kan ID een merkbare hoeveelheid stroom zien, die zal toenemen zoals bepaald door Eq. 5.13.

Merk op dat we bij het definiëren van de punten over de overdrachtskarakteristieken van de afvoerkarakteristieken alleen rekening houden met de verzadigingsniveaus. Dit beperkt het werkgebied tot VDS-waarden die hoger zijn dan de verzadigingsniveaus zoals vastgesteld door Eq. (5.12).

MOSFET's van het p-Channel Enhancement-type

De structuur van een MOSFET van het p-kanaalverbeteringstype zoals getoond in Fig. 5.37a is precies het tegenovergestelde van die getoond in Fig. 5.31.

Dit betekent dat je nu ontdekt dat een n-type substraat en p-gedoteerde gebieden onder de afvoer- en bronverbindingen zijn.

De klemmen blijven zoals vastgesteld, maar elk van de stroomrichtingen en de spanningspolariteiten zijn omgekeerd.

De afvoerkarakteristieken kunnen eruit zien zoals weergegeven in Fig. 5.37c, met toenemende stroomhoeveelheden veroorzaakt door een steeds negatievere grootte van VGS.

De overdrachtskarakteristieken zouden de spiegelindruk zijn (rond de ID-as) van de overdrachtscurve van Fig. 5.35, waarbij de ID toeneemt met steeds meer negatieve waarden van VGS boven VT, zoals weergegeven in Fig. 5.37b. Vergelijkingen (5.11) tot en met (5.14) zijn op dezelfde manier geschikt voor p-kanaalapparaten.

Referenties:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Vorige: Anti Spy RF Detector Circuit - Wireless Bug Detector Volgende: Overdrachtkenmerken