De fasevergrendelde lus is een van de basisblokken in moderne elektronische systemen. Het wordt over het algemeen gebruikt in multimedia, communicatie en in vele andere toepassingen. Er zijn twee verschillende soorten PLL's: lineair en niet-lineair. Het niet-lineaire is moeilijk en ingewikkeld om in de echte wereld te ontwerpen, maar de theorie van lineaire besturing is goed gemodelleerd in analoge PLL's. De PLL heeft bewezen dat een lineair model voldoende is voor de meeste elektronische toepassingen.

Wat is een Phase-Locked Loop?

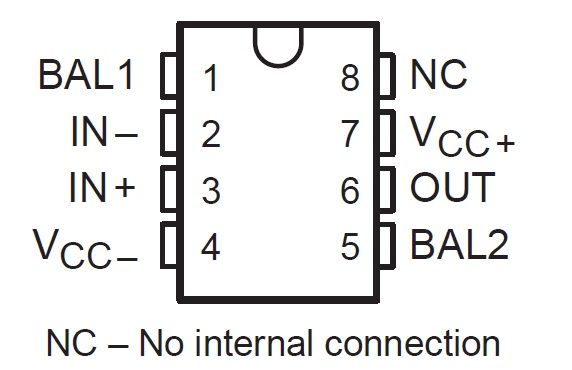

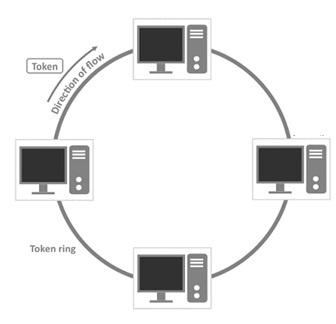

Een fasevergrendelde lus bestaat uit een fasedetector en een spanningsgestuurde oscillator. De uitgang van de fasedetector is de ingang van de spanningsgestuurde oscillator (VCO) en de uitgang van de VCO is verbonden met een van de ingangen van een fasedetector die hieronder in het basisblokschema wordt weergegeven. Wanneer deze twee apparaten aan elkaar worden toegevoerd, vormt de lus.

BASISDIAGRAM VAN FASE VERGRENDELDE LUS

Blokschema en werkingsprincipe van PLL

De fasevergrendelde lus bestaat uit een fasedetector, a spanningsgestuurde oscillator en daartussenin is een laagdoorlaatfilter bevestigd. Het ingangssignaal ‘Vi’ met een ingangsfrequentie ‘Fi’ wordt opgevangen door een fasedetector. In feite is de fasedetector een vergelijker die de ingangsfrequentie fi vergelijkt met de feedbackfrequentie fo. De output van de fasedetector is (fi + fo) wat een gelijkspanning is. De uit de fasedetector, d.w.z. gelijkspanning wordt ingevoerd naar het laagdoorlaatfilter (LPF), het verwijdert de hoogfrequente ruis en produceert een constant gelijkstroomniveau, d.w.z. Fi-Fo. De Vf is ook een dynamisch kenmerk van de PLL.

PLL-blokschema

De output van het laagdoorlaatfilter, d.w.z. het DC-niveau, wordt doorgegeven aan de VCO. Het ingangssignaal is recht evenredig met de uitgangsfrequentie van de VCO (fo). De ingangs- en uitgangsfrequenties worden vergeleken en aangepast via de terugkoppellus totdat de uitgangsfrequentie gelijk is aan de ingangsfrequentie. Daarom werkt de PLL als free running, capture en phase lock.

Als er geen ingangsspanning wordt aangelegd, is er sprake van een vrijlopende trap. Zodra de ingangsfrequentie die op de VOC wordt toegepast, verandert en een uitgangsfrequentie ter vergelijking produceert, wordt dit een capture-fase genoemd. De onderstaande afbeelding toont het blokschema van de PLL.

Fasevergrendelde lusdetector

De fasevergrendelde lusdetector vergelijkt de ingangsfrequentie en de uitgangsfrequentie van de VCO om een gelijkspanning te produceren die recht evenredig is met het faseverschil tussen de twee frequenties. De analoge en digitale signalen worden gebruikt in de fasevergrendelde lus. De meeste monolithische PLL geïntegreerde schakelingen gebruik een analoge fasedetector en de meeste fasedetectoren zijn van het digitale type. Een dubbel gebalanceerd mengcircuit wordt vaak gebruikt in analoge fasedetectoren. Enkele veel voorkomende fasedetectoren worden hieronder gegeven:

Exclusieve OF-fasedetector

Een exclusieve OF-fasedetector is van het type CMOS IC 4070. De ingangs- en uitgangsfrequenties worden toegepast op de EX OF-fasedetector. Om de uitvoer hoog te krijgen, moet ten minste één invoer laag zijn en de andere uitvoercondities zijn laag, wat wordt weergegeven in de onderstaande waarheidstabel. Laten we eens kijken naar de golfvorm, de ingangs- en uitgangsfrequenties, d.w.z. fi en fo hebben een faseverschil van 0 graden. Dan is de DC-uitgangsspanning van de comparator een functie van het faseverschil tussen de twee ingangen.

| worden | voor | Vdc |

laag | laag | laag |

laag | hoog | hoog |

hoog | Laag | hoog |

Hoog | Hoog | laag |

De functies van het faseverschil tussen de fi en fo zijn zoals weergegeven in de grafiek van de DC-uitgangsspanning. Als de fasedetector 180 graden is, is de uitgangsspanning maximaal. Als zowel de ingangs- als uitgangsfrequenties blokgolf zijn, worden dit type fasedetectoren gebruikt.

Exclusieve OF-fasedetector

Edge Trigger Phase Detector

Een flanktrigger-fasedetector wordt gebruikt wanneer de ingangs- en uitgangsfrequenties in pulsgolfvorm zijn, wat minder is dan 50% inschakelduur. De R-S flip-flop wordt gebruikt voor de fasedetectoren, zoals weergegeven in de onderstaande afbeelding. Van R-S slipper zijn de twee NOR-poorten kruislings gekoppeld. De uitgang van de fasedetector kan zijn logische toestand veranderen door de R-S-flip-flop te activeren. De positieve flank van de ingangs- en uitgangsfrequenties kan de uitgang van de fasedetector veranderen.

Edge Trigger Phase Detector

Monolithische fasedetector

Een monolithische fasedetector is van het CMOS-type, d.w.z. IC 4044. Hij wordt in hoge mate gecompenseerd door de harmonische gevoeligheid en de duty-cycle-problemen worden opgegeven omdat de schakeling alleen kan reageren op de overgang van het ingangssignaal. In kritische toepassingen is het de meest koortsige fasedetector. De onafhankelijke variaties van de amplitude zijn vrij van de fasefout, de uitgangsfoutspanning en de duty-cycle van de ingangsgolfvormen.

Toepassingen van Phase-Locked Loop

- FM-demodulatienetwerken voor FM-operaties

- Het wordt gebruikt in motortoerentalregelingen en volgfilters.

- Het wordt gebruikt in frequentieverschuivende decoderingen voor demodulatie draaggolffrequenties.

- Het wordt in de tijd gebruikt voor digitale converters.

- Het wordt gebruikt voor het verminderen van jitter, het onderdrukken van scheeftrekken en het herstel van de klok.

Dit gaat allemaal over het werk- en werkingsprincipe van de fasevergrendelde lus en zijn toepassingen. We hopen dat de informatie in het artikel nuttig voor u is om iets over het project te weten en het te begrijpen. Bovendien, als u vragen heeft over dit artikel en verder elektrische en elektronische projecten je kunt reageren in het onderstaande gedeelte. Hier is een vraag voor u, wat is de beste manier om de PLL voor stabiliteit te simuleren?

Fotocredits:

- Blokschema van PLL circuit vandaag

- Exclusieve OF-fasedetector sanfoundry

- Edge Trigger Phase Detector LEARNABOUT-ELEKTRONICA