RISC V is een Instruction set-architectuur ontwikkeld door de University of California, Berkeley. Het concept van RISC werd ingegeven door de waarheid dat de meeste processorinstructies niet door de meeste computerprogramma's werden gebruikt. Er werd dus onnodige decoderingslogica gebruikt in de ontwerpen van verwerkers , verbruiken meer stroom en oppervlakte. Om de instructieset te verkorten & meer te investeren in registermiddelen, is de RISC V-processor werd geïmplementeerd.

Deze technologie werd opgemerkt door veel techgiganten en start-ups omdat het volledig open source en gratis is. De meeste soorten processors zijn verkrijgbaar met een licentieovereenkomst, maar met dit type processor; iedereen kan zijn nieuwe processorontwerpen maken. Dus dit artikel bespreekt een overzicht van een RISC V-processor - werken en zijn toepassingen.

Wat is een RISC V-processor?

In de RISC V-processor staat de term RISC voor 'gereduceerde instructiesetcomputer', die weinig computerinstructies uitvoert, terwijl 'V' staat voor de 5e generatie. Het is een open-source hardware ISA (instruction set architecture) gebaseerd op het gevestigde principe van: RISICO .

In vergelijking met andere ISA-ontwerpen is deze ISA beschikbaar met een open source-licentie. Een aantal productiebedrijven heeft dus RISC-V-hardware aangekondigd en geleverd, met open-source besturingssystemen.

Dit is een nieuwe architectuur en is beschikbaar in open, niet-beperkende en gratis licenties. Deze processor heeft uitgebreide ondersteuning van chip- en apparaatfabrikanten. Het is dus voornamelijk ontworpen om vrij uitbreidbaar en aanpasbaar te zijn voor gebruik in veel toepassingen.

RISC V-geschiedenis

De RISC is rond 1980 uitgevonden door Prof. David Patterson aan de University of California, Berkeley. De Prof. David met Prof. John Hennessy dienden hun inspanningen in in twee boeken, namelijk 'Computer Organization and Design' & 'Computer Architecture aan de Stanford University. Dus ontvingen ze de ACM A.M. Turingprijs in het jaar 2017.

Van het jaar 1980 tot het jaar 2010 werd het ontwikkelingsonderzoek van de vijfde generatie van de RISC gestart en werd uiteindelijk geïdentificeerd als RISC-V, wat wordt uitgesproken als risico vijf.

RISC V Architectuur & Werken

De RV12 RISC V-architectuur wordt hieronder weergegeven. De RV12 is zeer configureerbaar met een single-core RV32I en RV64I compatibele RISC CPU die wordt gebruikt in embedded velden. De RV12 komt ook uit een 32- of 64-bit CPU-familie, afhankelijk van de industriële standaard RISC-V-instructieset.

De RV12 voert eenvoudigweg een Harvard-architectuur uit voor gelijktijdige toegang tot instructies en gegevensgeheugen. Het bevat ook een 6-traps pijplijn die helpt bij het optimaliseren van overlappingen tussen de uitvoering en geheugentoegangen om de efficiëntie te verbeteren. Deze architectuur omvat voornamelijk Branch Prediction, Data Cache, Debug Unit, Instruction Cache en optionele Multiplier of Divider Units.

De belangrijkste kenmerken van RV12 RISC V zijn de volgende.

- Het is een industriestandaard instructieset.

- Geparametriseerd met 32 of 64 bit data.

- Het heeft precieze en snelle interrupts.

- Aangepaste instructies maken de toevoeging van eigen hardwareversnellers mogelijk.

- Uitvoering van een enkele cyclus.

- Zes-traps pijplijn met optimalisatie gevouwen.

- Ondersteuning met geheugenbescherming.

- Optionele of geparametriseerde caches.

- Extreem geparametriseerd.

- Gebruikers kunnen 32/64-bit data & Branch Prediction Unit selecteren.

- Gebruikers kunnen instructie-/datacaches selecteren.

- Door de gebruiker te selecteren structuur, grootte en architectuur van cache.

- Hardware Divider of Multiplier Ondersteuning door door de gebruiker gedefinieerde latentie.

- De busarchitectuur is flexibel en ondersteunt Wishbone & AHB.

- Dit ontwerp optimaliseert de kracht en het formaat.

- Het ontwerp is volledig geparametriseerd, wat zorgt voor prestatie- of vermogenscompromissen.

- Gated CLK-ontwerp om het vermogen te verminderen.

- Software-ondersteuning volgens industriestandaard.

- Architectuursimulator.

- Eclipse IDE wordt gebruikt voor Linux/Windows.

De RISC V-uitvoeringspijplijn

Het omvat vijf fasen zoals IF (instructie ophalen), ID (instructie decoderen), EX (uitvoeren), MEM (geheugentoegang) en WB (registratie terugschrijven).

Instructie Ophalen

In Instruction Fetch of IF-fase wordt een enkele instructie gelezen uit de programmateller (PC) en het instructiegeheugen, die wordt bijgewerkt naar de volgende instructie.

Instructie Pre-decoderen

Zodra RVC-ondersteuning is toegestaan, zal de pre-decodeerfase van de instructie een 16-bits gecomprimeerde instructie decoderen in een native 32-bits instructie.

Instructie Decoderen:

In de Instruction Decode (ID)-fase is het registerbestand toegestaan en worden de bypass-controles beslist.

uitvoeren

In de Execute-fase wordt het resultaat berekend voor een ALU-, DIV-, MUL-instructie, het toegestane geheugen voor een Store- of Load-instructie en worden vertakkingen en sprongen gemeten tegen hun verwachte resultaten.

Geheugen

In deze geheugenfase wordt het geheugen benaderd via de pijplijn. Het opnemen van deze fase zorgt voor hoge prestaties van de pijpleiding.

Terugschrijven

In deze fase wordt het resultaat van de fase Uitvoering in het registerbestand geschreven.

Takvoorspeller

Deze processor bevat een vertakkingsvoorspellingseenheid of BPU die wordt gebruikt om gegevens uit het verleden op te slaan om de RISC V-processor te begeleiden bij het beslissen of een specifieke vertakking wordt genomen of niet. Deze voorspellingsgegevens worden eenvoudig bijgewerkt zodra de vertakking wordt uitgevoerd.

Deze unit bevat verschillende parameters die zijn gedrag bepalen. HAS_BPU wordt bijvoorbeeld gebruikt om te bepalen of een vertakking voorspelt dat een eenheid aanwezig is, BPU_GLOBAL_BITS zal bepalen hoeveel verleden bits moeten worden gebruikt en BPU_LOCAL_BITS zal bepalen hoeveel van de LSB van de programmateller moeten worden gebruikt. De combinatie van BPU_LOCAL_BITS & BPU_GLOBAL_BITS zal een vector creëren die voornamelijk wordt gebruikt om de Branch-Prediction-Table te adresseren.

Gegevenscache

Dit wordt voornamelijk gebruikt om de toegang tot gegevensgeheugen te versnellen door nieuw geopende geheugenlocaties te bufferen. Dit kan toegang tot halfwoord, byte en woord verwerken wanneer XLEN = 32 als ze zich op hun eigen grenzen bevinden. Het is ook in staat om toegangen van halve woorden, bytes, woorden en dubbele woorden te verwerken wanneer XLEN=64 als ze zich op hun eigen grenzen bevinden.

Tijdens een cachemisser kan een heel blok worden teruggeschreven naar het geheugen, dus indien nodig kan een nieuw blok in de cache worden geladen. De gegevenscache wordt uitgeschakeld door DCACHE_SIZE in te stellen op nul. Daarna zijn geheugenlocaties direct toegankelijk via de Gegevensinterface .

Instructiecache

Dit wordt voornamelijk gebruikt om het ophalen van instructies te versnellen door nieuw opgehaalde instructies te bufferen. Deze cache wordt gebruikt om één pakket op te halen voor elke cyclus op een 16-bits grens, maar niet over een blokgrens. Tijdens een cachemisser kan een heel blok uit het instructiegeheugen worden geladen. De configuratie van deze cache kan worden gedaan op basis van de behoeften van de gebruiker. De grootte van de cache, het vervangingsalgoritme en de bloklengte zijn configureerbaar.

De instructiecyclus wordt uitgeschakeld door ICACHE_SIZE op nul in te stellen. Daarna worden pakketjes direct uit het geheugen gehaald via de Instructie-interface.

Foutopsporingseenheid

De Debug Unit zorgt ervoor dat de Debug-omgeving kan stoppen en de CPU kan onderzoeken. De belangrijkste kenmerken hiervan zijn Branch Tracing, Single Step Tracing tot 8 Hardware Breakpoints.

Registreer bestand

Dit is ontworpen met 32 registerlocaties van X0 tot X31 waarbij X9 Register altijd nul is. Het registerbestand bevat 1-schrijfpoorten en 2-leespoorten.

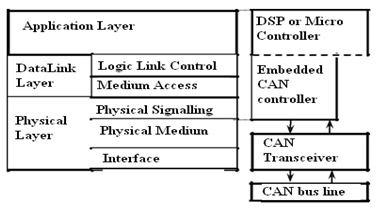

Configureerbare interface

Dit is een externe interface waarbij deze processor verschillende externe businterfaces ondersteunt.

Hoe werkt RISC V?

RISC-V is een instructiesetarchitectuur die is geworteld in de RISC-principes (Reduced Instructions Set Computer). Deze processor is zeer uniek en ook revolutionair omdat het een gratis, veelgebruikte en open-source ISA is waar hardware kan worden ontwikkeld, de software kan worden geporteerd en processors kunnen worden ontworpen om dit te ondersteunen.

Verschil Z/W RISC V versus MIPS

Het verschil tussen RISC V en MIPS omvat het volgende.

|

RISC V |

MIPS |

| De term RISC V staat voor Reduced Instruction Set Computer waarbij 'V' de vijfde generatie is. | De term 'MIPS' staat voor 'miljoen instructies per seconde'. |

| RISC-V staat de fabrikanten van kleinere apparaten eenvoudig toe om hardware te ontwerpen zonder te betalen. | Met MIPS kan de fabrikant de snelheid van de processor meten door te betalen omdat het niet gratis is. |

| MIPS is efficiënt dood. | RISC-V is niet efficiënt dood. |

| Deze processor geeft vertakkingsinstructies voor het vergelijken van twee registers. | MIPS is afhankelijk van een vergelijkingsinstructie die een register naar 1 of 0 lokaliseert op basis van het feit of het contrast waar is. |

| ISA-coderingsschema is vast en variabel in RISC V. | ISA-coderingsschema is opgelost in MIPS |

| De grootte van de instructieset is 16-bits of 32-bits of 64-bits of 128-bits. | De grootte van de instructieset is 32-bits of 64-bits. |

| Het heeft 32 registers voor algemene doeleinden en drijvende komma's | Het heeft 31 registers voor algemene doeleinden en drijvende komma's. |

| Het heeft 26 enkele en dubbele precisie drijvende-kommabewerkingen. | Het heeft 15 drijvende-kommabewerkingen met enkele en dubbele precisie. |

Verschil Z/W RISC V versus ARM

Het verschil tussen RISC V versus ARM omvat het volgende.

|

RISC V |

ARM |

| RISC-V is open source, dus er is geen licentie voor nodig. | ARM is een gesloten bron, dus het heeft een licentie nodig. |

| Het is een nieuw processorplatform, dus er is zeer weinig ondersteuning voor software- en programmeeromgevingen. | ARM heeft een zeer grote online community, die bibliotheken en structuren ondersteunt om de beoogde ontwerpers te helpen op verschillende platforms zoals microprocessors, microcontrollers en ook servers. |

| Op RISC V gebaseerde chips verbruiken 1 watt aan vermogen. | ARM-gebaseerde chips gebruiken minder dan 4 watt aan vermogen. |

| Het heeft een vast en variabel ISA-coderingssysteem. | Het heeft een vast ISA-coderingssysteem. |

| De grootte van de RISC V-instructieset varieert van 16-bits tot 128-bits. | De instructiegrootte varieert van 16-bits tot 64-bits. |

| Het bevat 32 registers voor algemene doeleinden en drijvende komma's. | Het bevat 31 registers voor algemene doeleinden en drijvende komma's. |

| Het heeft 26 enkele precisie drijvende-kommabewerkingen. | Het heeft 33 enkele precisie drijvende-kommabewerkingen. |

| Het heeft 26-dubbele precisie drijvende-kommabewerkingen. | Het heeft 29-dubbele precisie drijvende-kommabewerkingen. |

RISC V Verilog-code

De verilog-code van het instructiegeheugen voor RISC wordt hieronder weergegeven.

// Verilog-code voor RISC-processor

// Verilog-code voor instructiegeheugen

module Instructie_Geheugen(

invoer[15:0] pc,

uitvoer [15:0] instructie

);

reg [`col – 1:0] geheugen [`row_i – 1:0];

draad [3: 0] rom_addr = pc[4: 1];

voorletter

beginnen

$readmemb(“./test/test.prog”, geheugen,0,14);

einde

wijs instructie toe = geheugen [rom_addr];

eindmodule

Verilog-code voor de 16-bits RISC V-processor:

module Risc_16_bit(

invoer clk

);

draadsprong,bne,beq,mem_read,mem_write,alu_src,reg_dst,mem_to_reg,reg_write;

draad[1:0] alu_op;

draad [3:0] opcode;

// Gegevenspad

Datapath_Unit DU

(

.clk(clk),

.Spring Spring),

.kikker (kikker),

.mem_read(mem_read),

.mem_write (mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.alu_op(alu_op),

.opcode(opcode)

);

// besturingseenheid

Control_Unit controle

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.alu_op(alu_op),

.Spring Spring),

.bne(bne),

.kikker (kikker),

.mem_read(mem_read),

.mem_write (mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

);

eindmodule

Instructie sets

De RISC V instructiesets worden hieronder besproken.

Rekenkundige bewerkingen

De rekenkundige bewerkingen van RISC worden hieronder vermeld.

| ezelsbruggetje | Type | Instructie | Beschrijving |

| TOEVOEGEN rd, rs1, rs2 |

R |

Toevoegen | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

R |

Aftrekken | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

l |

Onmiddellijk toevoegen | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

R |

Stel minder in dan | rdß rs1 -< rs2 |

| SLTI rd, rs1, imm12 |

l |

Minder dan onmiddellijk instellen | rdß rs1 -< imm12 |

| SLTU rd, rs1, rs2 |

R |

Minder dan unsigned instellen | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

l |

Set minder dan onmiddellijk unsigned | rdß rs1 -< imm12 |

| LUI rd, imm20 |

IN |

Bovenste onmiddellijk laden | rdß imm20<<12 |

| AUIP rd, imm20 |

IN |

Voeg bovenste onmiddellijk toe aan pc | rdß PC+imm20<<12 |

Logische bewerkingen

De logische bewerkingen van RISC V worden hieronder vermeld.

| ezelsbruggetje | Type | Instructie | Beschrijving |

| EN rd, rs1, rs2 |

R |

EN | rdß rs1 & rs2 |

| OF rd, rs1, rs2 |

R |

OF | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

R |

VRIJ | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

l |

EN onmiddellijk | rdß rs1 & imm2 |

| ORI rd, rs1, imm12 |

l |

OF onmiddellijk | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

l |

XOR onmiddellijk | rdß rs1 ^ rs2 |

| SLL rd, rs1, rs2 |

R |

Shift naar links logisch | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

R |

Shift rechts logisch | rdß rs1 >> rs2 |

| RAS rd, rs1, rs2 |

R |

Shift rechts rekenkunde | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

l |

Shift links logisch onmiddellijk | rdß rs1 << shamt |

| SRLI rd, rs1, shamt |

l |

Shift rechts logisch onmiddellijk | rdß rs1 >> shamt |

| SRAI rd, rs1, shamt |

l |

Shift naar rechts rekenkunde onmiddellijk | rdß rs1 >> shamt |

Laad-/opslagactiviteiten

De RISC V-laad-/opslagbewerkingen worden hieronder vermeld.

| ezelsbruggetje | Type | Instructie | Beschrijving |

| LD rd, imm12 (rs1) |

l |

Dubbelwoord laden | rdß mem [rs1 +imm12] |

| LW rd, imm12 (rs1) |

l |

Woord laden | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

l |

Halverwege laden | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

l |

Laadbyte | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

l |

Woord niet-ondertekend laden | rdß mem [rs1 +imm12] |

| LHU rd, imm12 (rs1) |

l |

Laad een half woord niet ondertekend | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

l |

Laad byte niet ondertekend | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

S |

Dubbel woord opslaan | rs2 naar mem [rs1 +imm12] |

| SW rs2, imm12 (rs1) |

S |

woord opslaan | rs2 (31:0) naar mem [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

S |

Halverwege bewaren | rs2 (15:0) naar mem [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

S |

Winkelbyte | rs2 (15:0) naar mem [rs1 +imm12] |

| SRAI rd, rs1, shamt |

l |

Shift naar rechts rekenkunde onmiddellijk | rs2 (7:0) naar mem [rs1 +imm12] |

Vertakkingsbewerkingen

De RISC V-vertakkingsactiviteiten worden hieronder vermeld.

| ezelsbruggetje | Type | Instructie | Beschrijving |

| BEQ rs1, rs2, imm12 |

SB |

Tak gelijk | Als rs1== rs2 PC (PC+imm12) |

| BNE rs1, rs2, imm12 |

SB |

Tak niet gelijk | Als rs1!= rs2 PC (PC+imm12) |

| BGE rs1, rs2, imm12 |

SB |

Tak groter dan of gelijk aan | Als rs1>= rs2 PC (PC+imm12) |

| BGEU rs1, rs2, imm12 |

SB |

Tak groter dan of gelijk aan unsigned | Als rs1>= rs2 PC (PC+imm12) |

| BLT rs1, rs2, imm12 |

SB |

Tak minder dan | Als rs1< rs2 PC (PC+imm12) |

| BLTU rs1, rs2, imm12 |

SB |

Vertakking minder dan unsigned | Als rs1< rs2 PC ß PC+imm12 <<1 |

| JAL rd, imm20 |

UJ |

Springen en koppelen | rdßPC+4 PCß PC+imm20 |

| JALR rd, imm12(rs1) |

l |

Jump and Link registreren | rdßPC+4 PC (rs1+imm12) |

Voordelen:

De voordelen van de RISC V-processor omvatten het volgende.

- Door RISCV te gebruiken, kunnen we ontwikkelingstijd, softwareontwikkeling, verificatie, enz.

- Deze processor heeft veel voordelen, zoals eenvoud, openheid, modulariteit, strak ontwerp en uitbreidbaarheid.

- Dit wordt ondersteund door verschillende taalcompilers zoals de GCC (GNU Compiler Collection), een gratis-softwarecompiler en via de Linux-besturingssysteem .

- Dit kan door bedrijven vrij worden gebruikt vanwege geen royalty's, geen licentiekosten en geen verplichtingen.

- De RISC-V-processor bevat geen nieuwe of innovatieve functies omdat hij simpelweg de gevestigde principes van RISC volgt.

- Net als bij verschillende andere ISA's definieert deze processorspecificatie eenvoudig verschillende niveaus van instructieset. Dit bevat dus 32- en 64-bit-varianten en extensies om ondersteuning te bieden voor drijvende-komma-instructies.

- Deze zijn gratis, eenvoudig, modulair, stabiel, enz.

nadelen

De nadelen van de RISC V-processor omvatten het volgende.

- Complexe instructies worden vaak gebruikt door compilers en programmeurs.

- De o/p van een RISC kan veranderen op basis van de code wanneer volgende instructies binnen een lus afhankelijk zijn van de eerdere instructie voor uitvoering.

- Deze processors moeten een verscheidenheid aan instructies snel opslaan, wat een grote cachegeheugenset vereist om tijdig op de instructie te reageren.

- De volledige functies, mogelijkheden en voordelen van RISC zijn voornamelijk afhankelijk van de architectuur.

Toepassingen

De toepassingen van de RISC V verwerker omvatten het volgende.

- RISC-V wordt gebruikt in embedded systemen, kunstmatige intelligentie en machine learning.

- Deze processors worden gebruikt in op hoge prestaties gebaseerde embedded systeemtoepassingen.

- Deze processor is geschikt voor gebruik in bepaalde gebieden, zoals edge computing, AI en opslagtoepassingen.

- RISC-V is belangrijk omdat het kleinere apparaatfabrikanten in staat stelt hardware te ontwerpen zonder te betalen.

- Deze processor stelt de onderzoekers en ontwikkelaars eenvoudig in staat om zowel te ontwerpen als te onderzoeken met een vrij beschikbare ISA- of instructiesetarchitectuur.

- De toepassingen van RISC V variëren van kleine embedded microcontrollers tot desktop-pc's en supercomputers, inclusief vectorprocessors.

Dit is dus een overzicht van een RISC V-processor – architectuur, werken met applicaties. Hier is een vraag voor u, wat is een CISC-processor?