De post bespreekt de pinout-functie en andere belangrijke specificaties van de IC 4043. Laten we eens kijken naar de volledige datasheet van deze zeer interessante chip.

Pinout-gegevensblad van IC 4043

Technisch gezien is de IC 4043 een quad set / reset (R / S) latch met 3 logische toestandsuitgangen.

Om preciezer te zijn heeft deze chip 4 sets ingangen (dat wil zeggen 8 input pinouts) en 4 corresponderende enkele outputs.

De 4 sets ingangen bestaan uit 4 paar set / reset-ingangen.

Voor elke set / reset hebben we één bijbehorende uitgang.

Al deze ingestelde reset-ingangen reageren op hoge logische signalen, waardoor een bistabiel effect ontstaat bij hun overeenkomstige uitgangspennen.

Bistabiele flip / flop

Bistabiel verwijst naar flip-flop-actie, met andere woorden een hoge puls naar de 'set'-ingang maakt de corresponderende uitgang hoog vanuit zijn oorspronkelijke lage toestand, en een hoge naar de reset-ingang keert de bovenstaande toestand terug van hoog naar laag.

Om de corresponderende uitgangen dus hoog te maken, moeten we een high toepassen op hun 'set'-ingangen en om de uitgangen weer laag te maken, moeten we gewoon nog een high toepassen op hun reset-ingangen.

Zo simpel is de werking van de input en output pinouts.

Daarnaast heeft de IC nog een interessante input-pinout OE, een gemeenschappelijke output-inschakel-pin-out.

Set / Reset-functie

Om de hierboven toegelichte instel / reset-acties in het IC mogelijk te maken, moet deze OE-ingang worden verbonden met logisch hoog of gewoon met Vdd (supply votage).

In de bovenstaande situatie is de output toegestaan met de gespecificeerde flip-flop-werking.

Als de OE-ingang is verbonden met aarde, bevriest de uitgang en produceert deze een hoge impedantierespons, die noch een lage noch een hoge toont, maar de ingang vergrendelt in een niet-reagerende geblokkeerde toestand, vandaar de naam 3 logic state-uitgang.

De OE-ingang kan dus worden gebruikt om de IC-werking uit te schakelen indien dit nodig is voor een bepaalde toepassing.

Het IC werkt het beste met voedingsspanningen van 5 tot 15V.

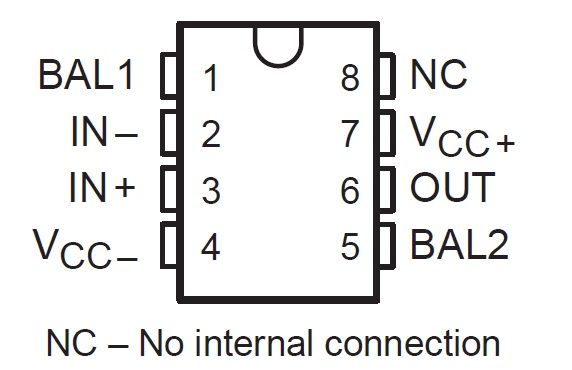

Laten we de pinout-functies en specificaties van de input-output van de IC 4043 samenvatten met de volgende gegevens:

- 1Q tot 4Q (Pins: 2, 9, 10, 1) 3-standen gebufferde vergrendelingsuitgang

- 1R tot 4R (pinnen: 3, 7, 11, 15) reset-ingang (actief HIGH)

- 1S tot 4S (Pins: 4, 6, 12, 14) set input (actief HIGH)

- OE (Pin: 5) gemeenschappelijke output vrijgave input

- VSS (Pin: 8) aarde voedingsspanning

- N.C. (Pin: 13) niet aangesloten

- VDD (Pin: 16) voedingsspanning

Meer updates:

In deze berichten proberen we de werking van de IC 4043 en IC 4044 te begrijpen door de verschillende specificaties, datasheet van de apparaten en hun pinout-opstelling te bestuderen.

In principe zijn beide varianten quad cross-coupled CMOS 3-state R / S of Reset / Set Latches. Quad betekent met 4 uitgangen die kunnen worden ingesteld of vergrendeld met een logisch hoog via een stuuringangssignaal, of gereset naar logische nul door een volgend ingangssignaal.

Dankzij de 3-statusfunctie kunnen de IC's worden bestuurd met behulp van 3 logica

Het fundamentele werkingsprincipe van IC 4043 en IC 4044 is hetzelfde als hierboven, het enige verschil is dat IC 4043B quad cross-coupled 3-state NOCH Latch en IC 4044B zijn quad cross-coupled 3-state NEN Klink.

Pinout-diagram

De volgende pinout-diagrammen van de IC's tonen de interne structuur en pinout-details van de apparaten:

In de bovenstaande diagrammen kunnen we zien dat elk van de typen 4 latches heeft met één uitgang en 2 individuele RESET / SET-ingangen. De functie van de ENABLE-pin voor alle SET / RESET-ingangen is identiek.

Een logische HOOG op de ENABLE-pin maakt het mogelijk dat de latch-toestanden worden verbonden met de relevante uitgangen, een logisch laag of 0 ontkoppelt de latch-toestanden van hun uitgangen, wat een volledig open circuit over de uitgangen veroorzaakt.

“xm-l t6 led ”

NOR Latch, NAND Latch Equivalente logische diagrammen

De volgende diagrammen tonen de equivalente vergrendelingen in de vorm van NOR- en NAND-vergrendelingen, die aanwezig zijn in elk van de 4 vergrendelingen van de individuele IC's.

Zoals we kunnen zien, wordt elk van de vergrendelingsblokken bestuurd met behulp van 3 logische besturingsingangen, namelijk SET, RESET en ENABLE, daarom is de uitgang afhankelijk van deze 3 ingangstoestanden. De waarheidstabel voor deze 3 logische toestanden kan worden geleerd uit het volgende diagram:

In de bovenstaande waarheidstabel kan de volledige vorm van de verschillende afgekorte symbolische alfabetten als volgt worden begrepen: S = SET Pin R = RESET Pin E = INSCHAKELEN Pin Q = OUTPUT Pin OC = Open Circuit NC = Geen verandering

De belangrijkste kenmerken van de IC 4043 en IC 4044 worden hieronder samengevat:

Praktische basiswerksimulatie van de SET / RESET- en ENABLE-pennen

Werkbeschrijving

Uit de bovenstaande simulatie-GIF kunnen we de werking van de quad latch-modules begrijpen met de volgende punten:

Wanneer de SET met een pin wordt toegepast met een positieve voeding, wordt de uitgang hoog en wordt vergrendeld, zelfs als het positieve potentieel van de SET-pin wordt verwijderd, zoals aangegeven door de rode LED (voorwaarts voorgespannen).

Wanneer de RESET-pin wordt toegepast met een positieve puls, wordt de vergrendeling verbroken en wordt de uitgang permanent LAAG, zelfs als het positieve wordt verwijderd uit de RESET-pin. Dit wordt aangegeven door het oplichten van de blauwe LED.

De bovenstaande bewerkingen kunnen alleen worden geïmplementeerd zolang de ENABLE-pin van de IC een positief voedingspotentieel heeft. Wanneer aangesloten op een negatief of aardpotentiaal, wordt de uitgang van de vergrendeling open en reageert deze niet meer op de SET / RESET-bewerkingen.

Vorige: Weekdag programmeerbaar timercircuit Volgende: IC 4033 Pinouts, gegevensblad, applicatie