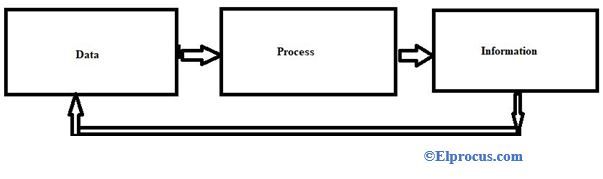

De MicroBlaze-processor is in 2002 ontwikkeld om verschillende gecompliceerde functies te integreren om te voldoen aan zowel nieuwe als groeiende marktvraag. De MicroBlaze-processor is dus een essentieel element binnen het low-end portfolio van Xilinx om snellere systeemontwikkeling mogelijk te maken die Artix®-7 bevat FPGA's , Spartan®-6, Zynq®-7000 AP SoC's. Deze processor is extreem configureerbaar, dus hij kan worden gebruikt als een embedded processor of microcontroller binnen FPGA's en ook als co-processor in de Zynq-7000 AP SoC's op basis van ARM Cortex-A9. Dit artikel geeft beknopte informatie over MicroBlaze-processor – architectuur en werken met applicaties.

Wat is Microblaze-processor?

De zachte microprocessor die voornamelijk is ontworpen voor FPGA's van Xilinx staat bekend als de MicroBlaze-processor. Deze processor is eenvoudig geïmplementeerd in de algemene geheugen- en logische structuur van FPGA's van Xilinx. Deze processor is vergelijkbaar met de DLX-architectuur op basis van RISC en heeft een flexibel verbindingssysteem zodat het verschillende embedded applicaties ondersteunt. De hoofd-I/O-bus en de AXI-interconnect van de MicroBlaze is een in het geheugen toegewezen transactiebus met een master-slave-faciliteit.

MicroBlaze gebruikt een speciale LMB-bus voor toegang tot lokaal geheugen en biedt snelle on-chip opslag. Veel onderdelen van deze processor kunnen door de gebruiker worden geconfigureerd, zoals de grootte van de cache, de diepte van de pijplijngeheugenbeheereenheid, ingesloten randapparatuur en businterfaces.

Microblaze-functies

De kenmerken van Microblaz e omvatten het volgende. Het heeft 32 registers voor algemene doeleinden.

- Het heeft 32-bits instructiewoorden inclusief 2 adresseringsmodi en 3 operanden.

- De adresbus is 32-bits.

- Het heeft een 3-traps pijpleiding of een 5-traps pijpleiding.

- Een ALU blok unit met een shifter.

- Harvard-architectuur omvat 32-bits gegevens- en adresbus.

- Gegevensinterface & LMB of lokale geheugenbusinstructie.

- AX14 en AX14 stream-interfaces.

- Drijvende-komma-eenheid en geheugenbeheereenheid.

- Het ondersteunt lockstep.

- Debug & trace-interface.

Microbaze-architectuur

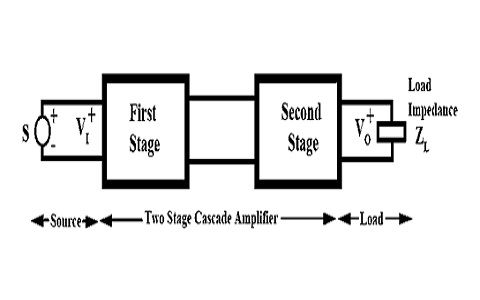

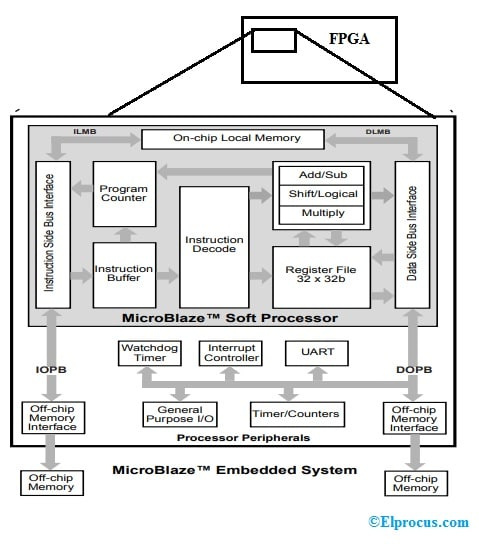

Het blokschema van de MicroBlaze-processor wordt hieronder weergegeven. Deze MicroBlaze-processor is uiterst aanpasbaar en ondersteunt meer dan 70 ontwerpopties. Deze architectuur toont permanente hardwarefuncties en configureerbare opties zoals de instructie- of gegevenscache, de geheugenbeheereenheid, de drijvende-komma-eenheid, enz.

Een ingebouwd systeem geassembleerd rond een MicroBlaze-processor omvat voornamelijk MicroBlaze Soft Processor Core, lokaal geheugen op de chip, standaard busverbindingen en OPB-randapparatuur (perifere bus op chip). Een MicroBlaze-processorsysteem varieert hoofdzakelijk van een processorkern door een lokaal geheugen tot een groot systeem met meerdere MicroBlaze verwerkers , extern geheugen en veel OPB-randapparatuur.

Zachte processorkern

De zachte processorkern van MicroBlaze staat centraal in het MicroBlaze embedded systeem. Dit is een zeer snelle en efficiënte 32-bits RISC-processor met de volgende kenmerken.

- De instructieset is orthogonaal.

- Aparte data- & instructiebussen.

- 32-bits registers voor algemene doeleinden.

- Het heeft een optionele complete 32-bit barrel shifter.

- Ingebouwde interfaces naar snel OCM of on-chip geheugen & IBM's industriestandaard OPB (On-chip Peripheral Bus).

Implementaties binnen Virtex-II en latere apparaten ondersteunen meerdere hardware.

Lokaal geheugen op chip

Het synchrone geheugen is een lokaal geheugen dat voornamelijk wordt gebruikt voor het toestaan van on-chip Block RAM.

Standaard busverbindingen

De businterfaces aan de instructie- en gegevenszijde omvatten een interface naar het lokale geheugen dat LMB (Local Memory Bus) wordt genoemd en een interface naar de On-chip Peripheral Bus van IBM. Dus we kunnen systemen ontwerpen die strikt vasthouden aan de Harvard-architectuur, anders kunnen we, om bronnen te delen, een enkele OPB gebruiken in combinatie via een busarbiter.

De lokale geheugenbus geeft een gegarandeerde ingang in één cyclus voor blok-RAM op de chip. Dit is een zeer efficiënt, eenvoudig en single-master busprotocol en het is perfect voor het koppelen van snel lokaal geheugen. De OPB of On-chip Peripheral Bus is een 32-bit brede multi-master bus die perfect is voor het verenigen van randapparatuur en extern geheugen tot de kern van de MicroBlaze-processor.

Perifere busrandapparatuur op chip

Het MicroBlaze-hardwaresysteem wordt aangevuld met OPB-randapparatuur om verschillende functies te bieden, zoals Watchdog Timer of Timebase, General-Purpose Timer of Counters, IC (Interrupt Controller), verschillende controllers zoals SRAM, Flash-geheugen, ZBT-geheugen, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, I/O voor algemeen gebruik, UART 16450/550 en Ethernet 10/100 MAC. Daarnaast kunnen we ook randapparatuur toevoegen en definiëren, voornamelijk voor aangepaste functies, anders een interface naar een ontwerp dat bestaat in de FPGA.

Microblaze-instructieset

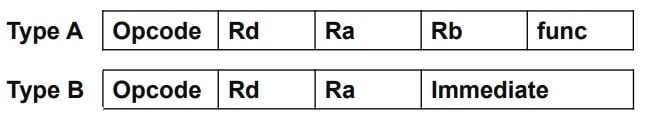

Microblaze-instructiesets zijn rekenkunde, logica, vertakking, laden/opslaan en andere. De grootte van alle instructies staat vast. Maximaal kunnen 3-registers als operanden worden opgegeven. Microblaze bevat twee instructieformaten Type A en Type B die hieronder worden weergegeven.

Type A instructieformaat wordt voornamelijk gebruikt voor register-registerinstructies. Het bevat dus de opcode, enkele bestemming en twee bronregisters. Type B-instructie-indeling wordt voornamelijk gebruikt voor register-directe instructies, waaronder de opcode, enkele bestemming en enkele bronregisters. & een 16-bits directe waardebron.

In de bovenstaande twee instructieformaten is de opcode een bewerkingscode, is Rd een bestemmingsregister dat is gecodeerd met 5-bits, Ra & Rb zijn bronregisters waarbij elk is gecodeerd met 5-bits en Immediate is een 16-bits waarde.

Rekenkundige instructies

De rekenkundige instructies van type A en type B worden hieronder gegeven.

Type A

|

TOEVOEGEN Rd, Ra, Rb toevoegen |

Rd = Ra+Rb, Draagvlag aangetast |

|

TOEVOEGEN K Rd, Ra, Rb Toevoegen en blijven dragen |

Rd = Ra+Rb, vlag niet beïnvloed |

| RSUB Rd, Ra, Rb Omgekeerd aftrekken |

Rd = R-Rb, vlag niet beïnvloed |

Type B

|

TOEVOEGEN I Rd, Ra, Imm voeg onmiddellijk toe |

Rd = Ra+tekenExtend32 (Imm) |

|

TOEVOEGEN IK Rd, Ra, Imm voeg onmiddellijk toe en blijf dragen |

Rd = Ra+ tekenExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm omgekeerd aftrekken met onmiddellijke |

Rd = Ra+ tekenExtend32 (Imm) -Ra |

| SRA Rd, Ra rekenkundige verschuiving naar rechts |

Rd = (Ra>>1) |

Logische instructies

De logische instructies van type A en type B worden hieronder gegeven.

Type A

|

OF Rd, Ra, Rb Logisch of |

Rd = Ra| Rb |

|

EN Rd,Ra,Rb Logische toevoeging |

Rd = Ra & Rb |

| XOR Rd, Ra, Rb Logoische xor |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Logisch en niet |

Rd = Ra & (Rb) |

Type B

|

ORI Rd, Ra, Imm logische OR met onmiddellijke |

Rd = Ra | tekenExtenden32 (Imm) |

| ANDI Rd, Ra, Imm logisch EN met onmiddellijk |

Rd = Ra & tekenExtend32 (Imm) |

| XORI Rd, Ra, Imm logoical XOR met onmiddellijke |

Rd = Ra ^ tekenExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Logisch EN NIET met onmiddellijk |

Rd = Ra & (signExtend32 (Imm)) |

Branch-instructies - onvoorwaardelijk

Wijzig het programmatellerregister

| BRID Imm vertakking onmiddellijk met onmiddellijke vertraging |

PC = PC+ tekenExtend32 (Imm) uitvoering van vertragingsslot toestaan |

| BRLID Rd, Imm vertakking en link onmiddellijk met onmiddellijke vertraging (functieaanroep) |

Rd = PC PC = PC+& tekenExtend32 (Imm) uitvoering van vertragingsslot toestaan |

| RTSD Ra, Imm terugkeer van subroutine |

PC = Ra + tekenExtend32 (Imm) uitvoering van vertragingsslot toestaan |

| RTID Ra, Imm terugkeer van interrupt |

PC = Ra + tekenExtend32 (Imm) uitvoering van vertragingsslot toestaan zet interrupt inschakelen in MSR |

Takinstructies - Onvoorwaardelijk1

Wijzig het register van de programmateller wanneer aan een voorwaarde is voldaan

| BEQI Ra, Imm tak indien gelijk |

PC = PC+ tekenExtend32 (Imm) Als Ra = = 0 |

| MASH Ra, Imm tak indien niet gelijk |

Rd = PC PC = PC+& tekenExtend32 (Imm) Als Ra! = 0 |

Branch-instructies - onvoorwaardelijk

Wijzig het register van de programmateller wanneer aan een voorwaarde is voldaan

| BLTI Ra, Imm tak indien lager dan |

PC = PC+ tekenExtend32 (Imm) Als Ra < 0 |

| BLEI Ra, Imm tak indien lager gelijk aan |

Rd = PC PC = PC+& tekenExtend32 (Imm) Als Ra!< = 0 |

| BGTI Ra, Imm tak indien groter dan |

PC = PC+ tekenExtend32 (Imm) Als Ra!> 0 |

| BGEI Ra, Imm tak indien groter gelijk aan |

PC = PC+tekenExtend32 (Imm) Als Ra!>= 0 |

Instructies voor laden/opslaan -Type A

| LW Rd, Ra, Rb Woord laden |

Adres = Ra+Rb Rd = *Adres |

| SW Rd, Ra, Rb Bewaar woord |

Adres – Ra+Rb *Adres = Rd |

Type B

| LWI Rd, Ra, Imn Woord onmiddellijk laden |

Adres = Ra + tekenExtend32 (Imm) Rd = *Adres |

| SW Rd, Ra, Imm Sla woord onmiddellijk op |

Adres = Ra + tekenExtend32 (Imm) *Adres = Rd |

Andere instructies:

| IMM, Imm onmiddellijk |

Breid de Imm van een voorgaande type B-instructie uit tot 32-bits. |

| MFS Rd, Sa Verplaatsen uit register voor speciale doeleinden |

Rd = Sa Sa- register voor speciale doeleinden, bronoperand

|

| MTS SD, Ra Verplaatsen naar register voor speciale doeleinden |

Sd = Ra Sd - register voor speciale doeleinden, bestemmingsoperand |

registreert

De architectuur van de MicroBlaze-processor is volledig orthogonaal en omvat 32-bits registers voor algemene doeleinden en 32-bits registers voor speciale doeleinden zoals Program Counter & Machine Status Register.

Pijplijnarchitectuur

MicroBlaze maakt gebruik van een 3-traps pijplijnarchitectuur, inclusief ophaal-, decoderings- en complete fasen. Automatisch worden de data forwarding, branches & pipeline stall bepaald binnen de hardware.

Laad- of winkelarchitectuur

MicroBlaze ondersteunt geheugen in drie dataformaten: 8 bits (Byte), 16 bits (Halfword) & 32 bits (Word). Geheugentoegangen zijn dus altijd afgestemd op de gegevensgrootte. Dit is een Big-Endian-processor die het adres van het Big-Endian-adres gebruikt, evenals labelconventies zodra het geheugen wordt gebruikt.

Onderbrekingen

Zodra een interrupt plaatsvindt, beëindigt deze processor de huidige uitvoering om het interruptverzoek te beheren via vertakking naar het interruptvectoradres en het instructie-adres op te slaan dat moet worden uitgevoerd. Deze processor stopt toekomstige onderbrekingen door de IE-vlag (Interrupt Enable) in de MSR (Machine Status Register) te wissen.

Hoe werkt Microblaze?

De MicroBlaze-processor ondersteunt 32-bits busbreedte en deze processorkern is een op RISC gebaseerde engine die een registerbestand bevat op basis van 32-bit LUT RAM via afzonderlijke instructies voor geheugen- en gegevenstoegang.

Deze processor ondersteunt eenvoudig zowel on-chip BlockRAM als extern geheugen. Vergelijkbaar met de IBM PowerPC; alle randapparatuur maakt dus gebruik van de vergelijkbare CoreConnect OPB-bus; de randapparatuur van de processor is goed afgestemd op PowerPC op Virtex-II Pro.

De MicroBlaze-processor biedt volledige flexibiliteit om de combinatie van geheugen, randapparatuur en interfacefuncties te kiezen die u het precieze systeem bieden dat u nodig hebt op een enkele FPGA tegen lagere kosten.

Verschil Z/W Microblaze versus Risc-V

De verschil tussen MicroBlaze en RISC v omvatten het volgende.

|

Microbrand |

Risc-V |

| Het is een zachte microprocessorkern die voornamelijk is ontworpen voor Xilinx FPGA.

|

RISC-V is een instructieset-architectuur die is geworteld in RISC-principes.

|

| Het maakt gebruik van de Harvard RISC-architectuur. | Het maakt gebruik van instructieset-architectuur. |

| De licentie is eigendom (Xilinx) | De licentie is open source. |

| De diepte van de pijpleiding is 3 of 5. | De diepte van de pijpleiding is 5. |

| De prestaties zijn 280 DMIP's. | De prestaties zijn 250 DMIP's. |

| De snelheid is 235 MHz. | De snelheid is 250 MHz. |

| Het heeft 1027 LUT's. | Het heeft 4125 LUT's. |

| De implementatie van de gebruikte technologie is Xilinx FPGA. | De implementatie van de gebruikte technologie is FPGA/ASIC. |

Voordelen van Microblaze

De voordelen van MicroBlaze omvatten het volgende.

- Het is economisch.

- Het is zeer configureerbaar.

- De prestaties zijn hoog in vergelijking met ARM.

- Het wordt ondersteund door een embedded development kit.

- Het is een zachte microprocessor kern.

- Om u te helpen bij het snel ordenen van uw applicatie, bevat deze processor drie vaste configuraties die gerelateerd zijn aan de bekende processorklassen microcontroller, realtime en applicatieprocessor.

Microblaze-toepassingen

De toepassingen van MicroBlaze omvatten het volgende.

- Deze processor voldoet aan veel verschillende toepassingsvereisten, zoals Industrieel, Automobiel, Medisch & Consumenten, enz.

- De toepassingen van MicroBlaze variëren van eenvoudige state-machines op basis van software tot complexe controllers die worden gebruikt in embedded toepassingen of op internet gebaseerde apparaten.

- Het is geoptimaliseerd voor embedded toepassingen zoals industriële besturing, kantoorautomatisering en automotive.

- De MicroBlaze kan communiceren met een groot aantal randapparatuur om in middelgrote toepassingen te passen.

- Het zachte karakter van deze processor maakt hem aanpasbaar voor verschillende toepassingen waar ontwerpers functies kunnen uitwisselen voor grootte om te voldoen aan prijs- en prestatiedoelen voor medische, automobiel-, industriële en beveiligingstoepassingen.

Dit gaat dus allemaal over een overzicht van de Microblaze verwerker. Dit is een volledig uitgeruste 32-bits programmeerbare RISC zachte processorkern. Deze processor voldoet aan verschillende vereisten op verschillende gebieden, zoals markten voor consumenten-, medische, industriële, automobiel- en communicatie-infrastructuur. Het is extreem configureerbaar, dus gebruikt als de embedded processor of microcontroller binnen FPGA's, anders als een co-processor voor de ARM. Hier is een vraag voor u, wat is FPGA?