De besturingseenheid is het hoofdonderdeel van een centrale verwerkingseenheid (CPU) in computers die de bewerkingen tijdens de uitvoering van een programma kan leiden door de processor /computer. De belangrijkste functie van de besturingseenheid is het ophalen en uitvoeren van instructies uit het geheugen van een computer. Het ontvangt de invoerinstructie / informatie van de gebruiker en zet deze om in stuursignalen , die vervolgens aan de CPU worden gegeven voor verdere uitvoering. Het is opgenomen als onderdeel van de Von Neumann-architectuur, ontwikkeld door John Neumann. Het is verantwoordelijk voor het leveren van de timingsignalen en besturingssignalen en stuurt de uitvoering van een programma door de CPU. Het is opgenomen als een intern onderdeel van de CPU in moderne computers. Dit artikel beschrijft volledige informatie over de besturingseenheid.

Wat is de regeleenheid?

De component die het ingangssignaal / informatie / instructie van de gebruiker ontvangt en omzet in stuursignalen voor uitvoering in de CPU. Het bestuurt en stuurt het hoofdgeheugen, de rekenkundige en logische eenheid (ALU), invoer- en uitvoerapparaten, en is ook verantwoordelijk voor de instructies die naar de CPU van een computer worden gestuurd. Het haalt de instructies op van de hoofd geheugen van een processor en verzonden naar het processorinstructieregister, dat registerinhoud bevat.

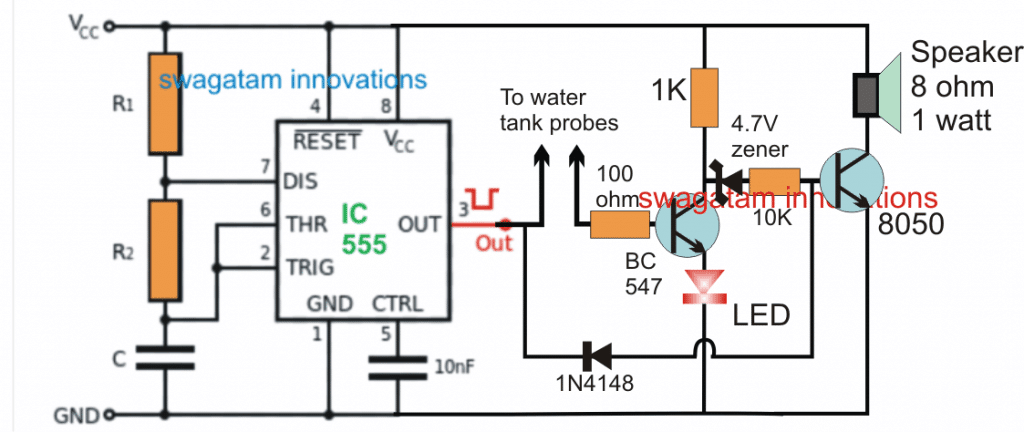

Blokschema regeleenheid

De besturingseenheid zet de invoer om in besturingssignalen en vervolgens verzonden naar de processor en stuurt de uitvoering van een programma. De bewerkingen die moeten worden uitgevoerd, worden aangestuurd door de processor op de computer. Voornamelijk Central Processing Unit (CPU) en Grafische verwerkingseenheid (GPU) vereisen een besturingseenheid als intern onderdeel. Het blokschema van de besturingseenheid is hierboven weergegeven.

Onderdelen van een besturingseenheid

De componenten van dit apparaat zijn instructie registreert , besturingssignalen binnen de CPU, besturingssignalen van / naar de bus, besturingsbus, ingangsvlaggen en kloksignalen.

De componenten van de bedrade besturingseenheid zijn instructieregister (bevat opcode en adresveld), timingeenheid, besturingstoestand generator , besturingssignaalgeneratiematrix en instructiedecoder.

De componenten van de Micro-geprogrammeerde besturingseenheid zijn de volgende adresgenerator, een besturingsadresregister, besturingsgeheugen en besturingsgegevensregister.

Functies

De functies van de besturingseenheid omvatten de volgende.

- Het stuurt de datastroom tussen de processor en andere apparaten.

- Het kan de instructies interpreteren en de gegevensstroom in de processor regelen.

- Het genereert de reeks stuursignalen uit de ontvangen instructies of opdrachten uit het instructieregister.

- Het heeft de verantwoordelijkheid om de uitvoeringseenheden zoals ALU, gegevensbuffers en registers in de CPU van een computer te besturen.

- Het heeft de mogelijkheid om resultaten op te halen, te decoderen, de uitvoering af te handelen en op te slaan.

- Het kan de gegevens niet verwerken en opslaan

- Om de gegevens over te dragen, communiceert het met de invoer- en uitvoerapparaten en bestuurt het alle eenheden van de computer.

Ontwerp van besturingseenheid

Het ontwerp hiervan kan worden gedaan met behulp van twee types van een besturingseenheid waaronder de volgende.

- Hardwire gebaseerd

- Microgeprogrammeerd gebaseerd (één niveau en twee niveaus)

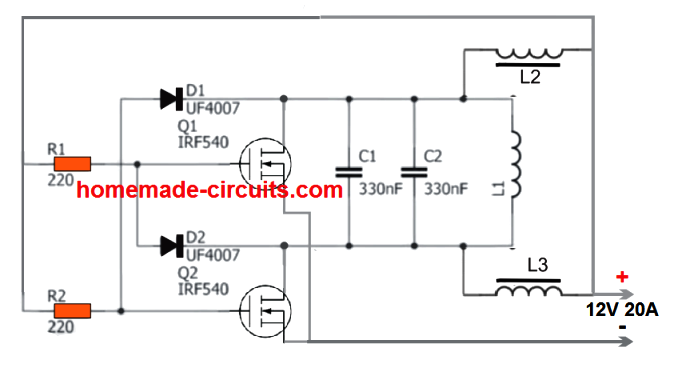

Bedrade besturingseenheid

Het basisontwerp van een bedrade besturingseenheid wordt hierboven weergegeven. Bij dit type worden de stuursignalen gegenereerd door een speciale hardware logisch circuit zonder enige verandering in de structuur van het circuit. Hierbij kan het gegenereerde signaal niet worden gewijzigd voor uitvoering in de processor.

De basisgegevens van een opcode (operatiecode van een instructie wordt naar de instructiedecoder gestuurd voor decodering. De instructie decoder is de set decoders om verschillende soorten gegevens in de opcode te decoderen. Dit resulteert in uitgangssignalen die waarden van actieve signalen bevatten die worden gegeven als invoer voor de matrixgenerator om stuursignalen te genereren voor de uitvoering van een programma door de processor van de computer.

Bedrade besturingseenheid

De matrixgenerator levert toestanden van de besturingseenheid en de signalen van de processor (interruptsignalen). Matrix is gebouwd als de programmeerbare logische reeks De besturingssignalen die door de matrixgenerator worden gegenereerd, worden gegeven als invoer voor de volgende generatormatrix en worden gecombineerd met de timingsignalen van de timingeenheid die rechthoekige patronen bevat.

Voor het ophalen van een nieuwe instructie gaat de besturingseenheid over in een eerste fase voor het uitvoeren van een nieuwe instructie. De besturingseenheid blijft in de beginfase of de eerste trap zolang de timingsignalen, ingangssignalen en instructietoestanden van een computer ongewijzigd blijven. De verandering in de toestand van de besturingseenheid kan worden verhoogd als er een verandering in een van de gegenereerde signalen optreedt.

Wanneer een extern signaal of onderbreking optreedt, gaat de besturingseenheid naar de volgende toestand en voert de verwerking van het onderbrekingssignaal uit. De vlaggen en statussen worden gebruikt om de gewenste statussen te selecteren om de uitvoeringscyclus van instructie uit te voeren.

In de laatste toestand haalt de besturingseenheid de volgende instructie op en stuurt de uitvoer naar de programmateller, vervolgens naar het geheugenadresregister, naar het bufferregister en vervolgens naar het instructieregister om de instructie te lezen. Ten slotte, als de laatste instructie (die wordt opgehaald door de besturingseenheid) eindinstructie is, gaat deze naar de bedrijfstoestand van de processor en wacht totdat de gebruiker het volgende programma leidt.

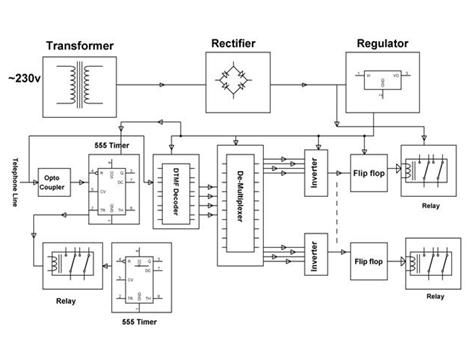

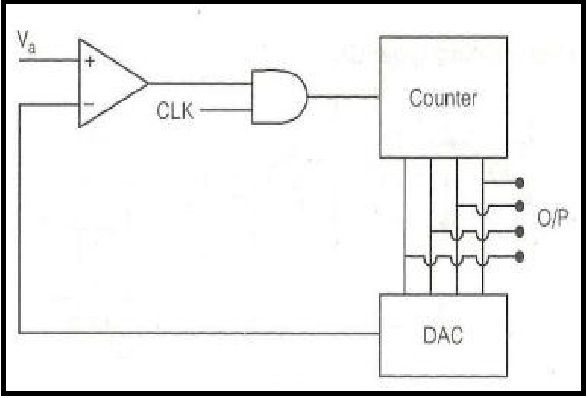

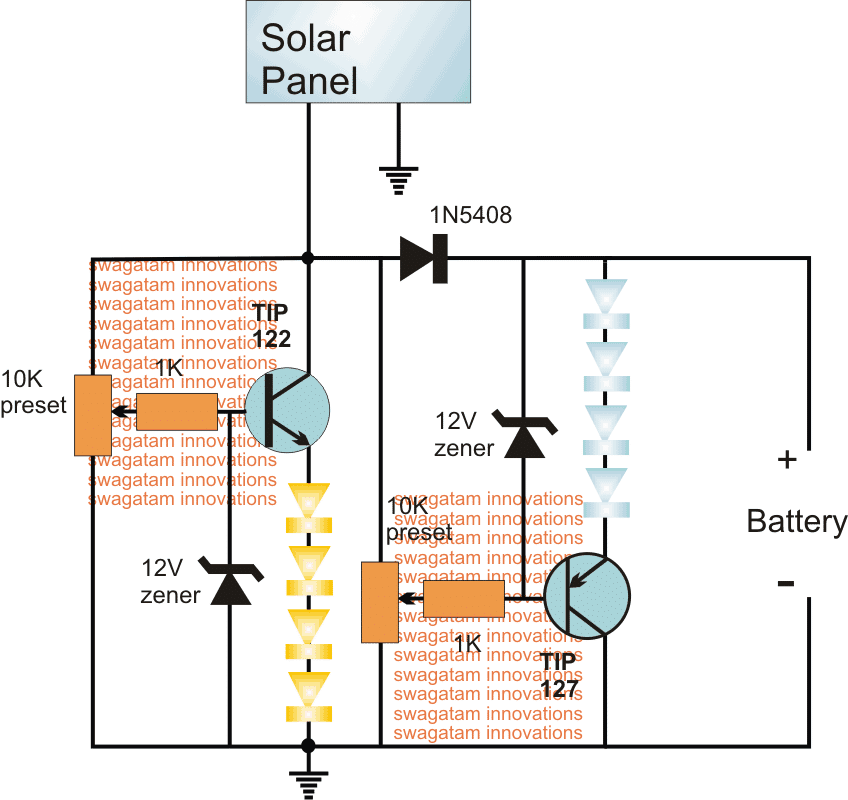

Micro geprogrammeerde besturingseenheid

In dit type wordt het besturingsgeheugen gebruikt om de besturingssignalen op te slaan die tijdens de uitvoering van een programma worden gecodeerd. Het stuursignaal wordt niet onmiddellijk gegenereerd en gedecodeerd omdat het microprogramma adresveld opslaat in het stuurgeheugen. Het hele proces is een enkel niveau.

De microbewerkingen worden gedaan voor het uitvoeren van micro-instructies in het programma. Het blokschema van de Micro geprogrammeerde besturingseenheid is hierboven weergegeven. Uit het diagram wordt het adres van de micro-instructie verkregen uit het adresregister van het stuurgeheugen. Alle info van de besturingseenheid wordt permanent opgeslagen in het besturingsgeheugen genaamd ROM.

Op microgeprogrammeerde gebaseerde besturingseenheid

De micro-instructie uit het stuurgeheugen wordt vastgehouden door het stuurregister. Aangezien de micro-instructie de vorm heeft van een controlewoord (bevat binaire controlewaarden), moeten er 1 of meer microbewerkingen worden uitgevoerd voor de gegevensverwerking.

Tijdens de uitvoering van micro-instructies berekende de volgende adresgenerator het volgende adres van de micro-instructie en stuurde deze vervolgens naar het stuuradresregister om de volgende micro-instructie te lezen.

De sequentie van microbewerkingen van een microprogramma wordt uitgevoerd door de volgende adresgenerator en fungeert als microprogrammasequencer om het sequentieadres te krijgen, d.w.z. gelezen uit het besturingsgeheugen.

Verilog-code voor de besturingseenheid

Verilog-code voor regeleenheid wordt hieronder weergegeven.

`include“ prj_definition.v ”

module CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_RITE, RF_DATA_RITE, RF_DATA_RITE, RF_DATA_RITE, RF_DATA_RITE)

// Uitgangssignalen

// Uitgangen voor registerbestand

uitvoer [`DATA_INDEX_LIMIT: 0] RF_DATA_W

uitvoer [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

output RF_READ, RF_WRITE

// Uitgangen voor ALU

uitvoer [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

uitvoer [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Uitgangen voor geheugen

uitvoer [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

output MEM_READ, MEM_WRITE

// Ingangssignalen

invoer [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

invoer ZERO, CLK, RST

// Inout signaal

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Staatsnetten

draad [2: 0] proc_state

// bevat programmatellerwaarde, slaat de huidige instructie op, stapel pointerregister

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] state, next_state

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK) ,. RST (RST))

altijd @ (posedge CLK)

beginnen

als (RST)

staat<= RST

anders

staat<= next_state

einde

altijd @ (staat)

beginnen

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

case (staat)

`PROC_FETCH: begin

next_state = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

einde

`PROC_DECODE: begin

next_state = `PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

einde

`PROC_EXE: begin

next_state = `PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

einde

`PROC_MEM: begin

next_state = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

einde

`PROC_WB: begin

next_state = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

einde

eindkast

einde

eindmodule

module PROC_SM (STATE, CLK, RST)

// lijst met ingangen

ingang CLK, RST

// lijst met uitgangen

output [2: 0] STATE

// invoerlijst

ingang CLK, RST

// uitvoerlijst

uitvoer STATE

reg [2: 0] STATE

reg [1: 0] staat

reg [1: 0] volgende_staat

reg PC_REG, INST_REG, SP_REF

`definieer PROC_FETCH 3’h0

'definieer PROC_DECODE 3’h1

`definieer PROC_EXE 3’h2

`definieer PROC_MEM 3’h3

`definieer PROC_WB 3’h4

// initiatie van staat

eerste

beginnen

state = 2’bxx

next_state = `PROC_FETCH

einde

// reset signaalverwerking

altijd @ (posedge RST)

beginnen

state = `PROC_FETCH

next_state = `PROC_FETCH

einde

altijd @ (posedge CLK)

beginnen

state = next_state

einde

altijd @ (staat)

beginnen

if (staat === `PROC_FETCH)

beginnen

next_state = `PROC_DECODE

print_instructie (INST_REG)

einde

if (staat === `PROC_DECODE)

beginnen

next_state = `PROC_EXE

einde

if (staat === `PROC_EXE)

beginnen

next_state = `PROC_MEM

print_instructie (SP_REF)

einde

if (staat === `PROC_MEM)

beginnen

next_state = `PROC_WB

einde

if (staat === `PROC_WB)

beginnen

next_state = `PROC_FETCH

print_instructie (PC_REG)

einde

einde

taak print_instructie

voer [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] opcode

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] direct reg [25: 0] adres

beginnen

// ontleed de instructie

// R-type

{opcode, rs, rt, rd, shamt, funct} = inst

// Ik typ

{opcode, rs, rt, onmiddellijke} = inst

// J-type

{opcode, adres} = inst

$ write ('@% 6dns -> [0X% 08h]', $ time, inst)

case (opcode) // R-Type

6’h00 : begin

case (functie)

6'h20: $ write ('add r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'22: $ write ('sub r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2c: $ write ('mul r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h24: $ write ('en r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h25: $ write ('of r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h27: $ write ('nor r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2a: $ write ('slt r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h00: $ write ('sll r [% 02d],% 2d, r [% 02d]', rs, shamt, rd)

6’h02: $ write ('srl r [% 02d], 0X% 02h, r [% 02d]', rs, shamt, rd)

6’h08: $ write ('jr r [% 02d]', rs)

standaard: $ write ('')

eindkast

einde

// Ik typ

6'h08: $ write ('addi r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

6’h1d: $ write ('muli r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

6’h0c: $ write ('andi r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

6’h0d: $ write ('ori r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

6’h0f: $ write ('lui r [% 02d], 0X% 04h', rt, onmiddellijk)

6’h0a: $ write ('slti r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

6’h04: $ write ('beq r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

6’h05: $ write ('bne r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

6’h23: $ write ('lw r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

6’h2b: $ write ('sw r [% 02d], r [% 02d], 0X% 04h', rs, rt, onmiddellijk)

// J-Type

6’h02: $ write ('jmp 0X% 07h', adres)

6’h03: $ write ('jal 0X% 07h', adres)

6’h1b: $ write ('push')

6’h1c: $ write ('pop')

standaard: $ write ('')

eindkast

$ write (' n')

einde

einde taak

einde module

Veelgestelde vragen

1). Wat is het werk van een besturingseenheid?

Het werk van de besturingseenheid is het sturen van de gegevensstroom of instructies voor de uitvoering door de processor van een computer. Het bestuurt, beheert en coördineert het hoofdgeheugen, ALU, registers, invoer- en uitvoereenheden. Het haalt de instructies op en genereert besturingssignalen voor de uitvoering.

2). Wat is het besturingsgeheugen?

Het stuurgeheugen is meestal RAM of ROM om het adres en de gegevens van het stuurregister op te slaan.

3). Wat is de Wilkes-regeleenheid?

De opeenvolgende en combinatieschakelingen van de bedrade besturingseenheid worden vervangen door de Wilkes besturingseenheid. Het gebruikt een opslageenheid om de instructiesreeksen van een microprogramma op te slaan.

4). Wat is een bedrade besturingseenheid?

De bedrade besturingseenheid genereert de besturingssignalen door bij elke klokpuls van de ene toestand naar de andere te gaan zonder enige fysieke verandering in het circuit. Het genereren van stuursignalen hangt af van het instructieregister, decoder en interruptsignalen.

5). Wat is het besturingsgeheugen?

De informatie van de besturingseenheid of gegevens wordt tijdelijk of permanent opgeslagen in het besturingsgeheugen.

Er zijn twee soorten besturingsgeheugen. Dit zijn Random Access Memory (RAM) en Read-Only Memory (ROM).

Dit gaat dus allemaal over de definitie, componenten, ontwerp, diagram, functies en soorten regeleenheid Hier is een vraag voor u: 'Wat is het doel van het controleadresregister?'