De veldeffecttransistor (FET) is een elektronisch apparaat waarin een elektrisch veld wordt gebruikt om de stroom te regelen. Om dit te implementeren wordt een potentiaalverschil aangelegd over de gate- en source-aansluitingen van het apparaat, waardoor de geleidbaarheid tussen de drain- en source-aansluitingen verandert, waardoor een gecontroleerde stroom over deze aansluitingen loopt.

FET's worden genoemd unipolaire transistors omdat deze zijn ontworpen om te werken als apparaten met een enkele drager. Er zijn verschillende soorten veldeffecttransistors beschikbaar.

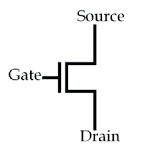

Symbool

De grafische symbolen voor de n-kanaals en p-kanaals JFET's kunnen in de volgende afbeeldingen worden weergegeven.

Je kunt duidelijk zien dat de pijl naar binnen wijst voor het n-kanaals apparaat om de richting aan te geven waarin ikG(poortstroom) wordt verondersteld te stromen wanneer de p-n-overgang naar voren is voorgespannen.

In het geval van een p-kanaalapparaat zijn de voorwaarden identiek behalve het verschil in de richting van het pijlsymbool.

Verschil tussen FET en BJT

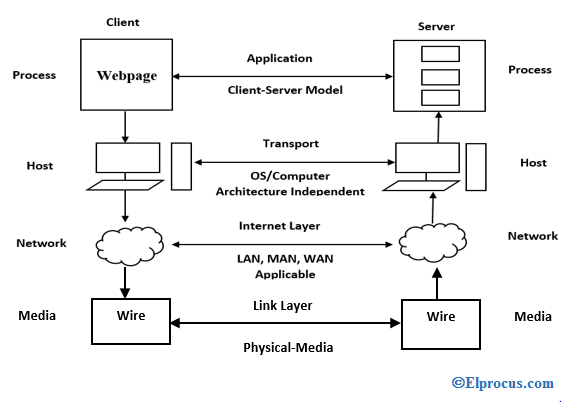

De veldeffecttransistor (FET) is een apparaat met drie aansluitingen dat is ontworpen voor een breed scala aan circuittoepassingen die op een hoog niveau die van de BJT-transistor aanvullen.

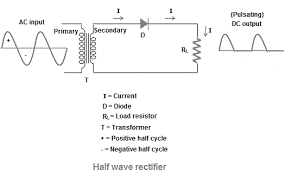

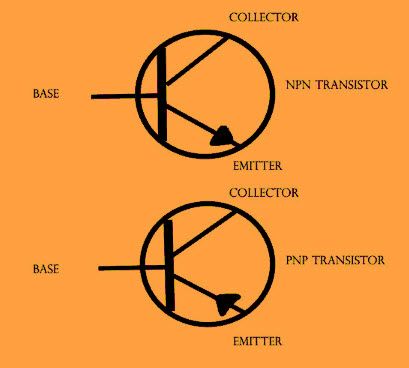

Hoewel u aanzienlijke verschillen zult vinden tussen BJT's en JFET's, zijn er in feite verschillende overeenkomende kenmerken waarover in de volgende discussies zal worden gesproken. Het belangrijkste verschil tussen deze apparaten is dat BJT een stroomgestuurd apparaat is zoals weergegeven in Fig. 5.1a, terwijl de JFET-transistor een spanningsgestuurd apparaat is zoals aangegeven in Fig. 5.1b.

Simpel gezegd, de huidige ICin Fig. 5.1a is een directe functie van het niveau van IB.Voor de FET is de stroom I een functie van de spanning VGSgegeven aan het ingangscircuit zoals getoond in Fig. 5.1b.

In beide gevallen wordt de stroom van het uitgangscircuit bepaald door een parameter van het ingangscircuit. In de ene situatie een stroomniveau en in de andere een aangelegde spanning.

Net als npn en pnp voor bipolaire transistors, vindt u n-kanaal en p-kanaal veldeffecttransistors. Maar u moet niet vergeten dat de BJT-transistor een bipolair apparaat is waarvan het voorvoegsel bi- aangeeft dat het geleidingsniveau een functie is van twee ladingsdragers, elektronen en gaten.

De FET daarentegen is een unipolair apparaat dat hangt uitsluitend af van ofwel elektron (n-kanaal) of gat (p-kanaal) geleiding.

De uitdrukking 'veldeffect' kan als volgt worden uitgelegd: we zijn ons allemaal bewust van de kracht van een permanente magneet om metaalvijlsel naar de magneet te trekken zonder enig fysiek contact. Op een vergelijkbare manier wordt binnen FET een elektrisch veld gecreëerd door de bestaande ladingen die het geleidingspad van het uitgangscircuit beïnvloeden zonder enig direct contact tussen de controlerende en gecontroleerde grootheden. Waarschijnlijk een van de meest cruciale kenmerken van de FET is de hoge ingangsimpedantie.

Variërend van een magnitude van 1 tot vele honderden megohm, overtreft het aanzienlijk de normale ingangsweerstandsbereiken van de BJT-configuraties, een uiterst belangrijk kenmerk bij het ontwikkelen van lineaire wisselstroomversterkermodellen.

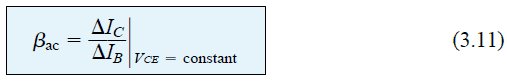

De BJT heeft echter een grotere gevoeligheid voor variaties in het ingangssignaal. Dit betekent dat de verandering in uitgangsstroom gewoonlijk significant meer is voor BJT's dan voor FET's voor dezelfde hoeveelheid verandering in hun ingangsspanningen.

Hierdoor kunnen standaard wisselspanningsversterkingen voor BJT-versterkers veel hoger zijn in vergelijking met FET's.

Over het algemeen zijn FET's aanzienlijk thermisch veerkrachtiger dan BJT's en hebben ze ook vaak een kleinere structuur in vergelijking met BJT's, waardoor ze specifiek geschikt zijn om in te bedden als geïntegreerde schakeling (IC)chips.

De structurele kenmerken van sommige FET's kunnen ervoor zorgen dat ze extra gevoelig zijn voor fysieke contacten dan BJT's.

Meer BJT / JFET-relatie

- Voor een BJT VWORDEN= 0,7 V is de belangrijkste factor voor het starten van een analyse van de configuratie.

- Evenzo is de parameter IG= 0 A is gewoonlijk het eerste dat in overweging wordt genomen voor de analyse van een JFET-circuit.

- Voor de BJT-configuratie IB.is vaak de eerste factor die moet worden bepaald.

- Evenzo is het voor de JFET meestal de VGS

In dit artikel zullen we ons concentreren op JFET's of junctie-veldeffecttransistors, in het volgende artikel zullen we ingaan op metaal-oxide-halfgeleider-veld-effcet-transistoren of MOS-FET.

CONSTRUCTIE EN KENMERKEN VAN JFET's

Zoals we eerder hebben geleerd, heeft een JFET 3 leads. Een van hen regelt de stroom tussen de andere twee.

Net als BJT's wordt ook in JFET's het n-kanaals apparaat prominenter gebruikt dan de p-kanaals tegenhangers, aangezien n apparaten doorgaans efficiënter en gebruiksvriendelijker zijn in vergelijking met het p-apparaat.

In de volgende afbeelding kunnen we de basisstructuur of constructie van een n-kanaals JFET zien. We kunnen zien dat de samenstelling van het n-type het belangrijkste kanaal vormt over de lagen van het p-type.

Het bovenste deel van het n-type kanaal is verbonden via een ohms contact met een terminal genaamd de drain (D), terwijl het onderste deel van hetzelfde kanaal ook is verbonden via een ohms contact met een andere terminal genaamd de source (S).

De paar p-type materialen zijn samen verbonden met de terminal die de poort (G) wordt genoemd. In wezen vinden we dat de drain- en source-aansluitingen zijn verbonden met de uiteinden van het n-type kanaal. De gate-aansluiting is verbonden met een paar p-kanaalmateriaal.

Als er geen spanning over een jfet wordt aangelegd, hebben de twee p-n-overgangen geen voorspanning. In deze situatie bestaat er een uitputtingsgebied op elk knooppunt, zoals aangegeven in de bovenstaande figuur, dat er vrij uitziet als een diode p-n-gebied zonder voorspanning.

Wateranalogie

De werkings- en besturingshandelingen van een JFET kunnen worden begrepen aan de hand van de volgende wateranalogie.

Hier kan de waterdruk worden vergeleken met de toegepaste spanningsgrootte van afvoer naar bron.

De stroming van water is te vergelijken met de stroming van elektronen. De monding van de kraan imiteert de bronterminal van de JFET, terwijl het bovenste gedeelte van de kraan waar het water naar binnen wordt gedwongen de afvoer van de JFET weergeeft.

De tap-knop werkt als de poort van de JFET. Met behulp van een ingangspotentiaal regelt het de stroom van elektronen (lading) van afvoer naar bron, net zoals de tapknop de stroom van water op de mondopening regelt.

Uit de JFET-structuur kunnen we zien dat de drain en de source-terminals zich aan de tegenovergestelde uiteinden van het n-kanaal bevinden, en aangezien de term is gebaseerd op elektronenstroom, kunnen we schrijven:

VGS= 0 V, VDSEen positieve waarde

In figuur 5.4 kunnen we een positieve spanning V zienDStoegepast over het n-kanaal. De poortterminal is direct verbonden met de bron om een conditie V te creërenGS= 0V. Dit maakt het mogelijk dat de poort en de bronaansluitingen op een identiek potentiaal zijn, en resulteert in een lagere uitputtingsgebied van elk p-materiaal, precies zoals we zien in het eerste diagram hierboven met een niet-voorspanningstoestand.

Zodra een spanning VDD(= VDS) wordt toegepast, worden elektronen naar de afvoeraansluiting getrokken, waardoor de conventionele stroom van de huidige ID wordt gegenereerd, zoals aangegeven in figuur 5.4.

De richting van de stroom van de lading laat zien dat de afvoerstroom en de bronstroom even groot zijn (I.D= IkSVolgens de omstandigheden die zijn weergegeven in figuur 5.4, ziet de stroom van de lading er vrij onbeperkt uit en wordt deze alleen beïnvloed door de weerstand van het n-kanaal tussen drain en de source.

U zult wellicht opmerken dat het uitputtingsgebied groter is rond het bovenste gedeelte van beide p-type materialen. Dit verschil in grootte van de regio wordt idealiter verklaard door de figuur 5.5. Laten we ons voorstellen dat we een uniforme weerstand hebben in het n-kanaal, deze zou kunnen worden opgesplitst in de secties die zijn aangegeven in figuur 5.5.

De huidige IDkan de spanningsbereiken door het kanaal opbouwen, zoals aangegeven in dezelfde afbeelding. Dientengevolge zal het bovenste gebied van het p-type materiaal in tegengestelde richting worden voorgespannen met een niveau van ongeveer 1,5 V, terwijl het onderste gebied slechts met 0,5 V in omgekeerde richting wordt voorgespannen.

Het punt dat de p-n-overgang in tegengestelde richting over het hele kanaal loopt, geeft aanleiding tot een poortstroom met nul ampère, zoals weergegeven in dezelfde figuur. Deze eigenschap die leidt tot IG= 0 A is een belangrijk kenmerk van de JFET.

Zoals VDSpotentieel wordt verhoogd van 0 tot enkele volt, de stroom neemt toe volgens de wet van Ohm en de plot van I.Dlijn 5DSkan er bewezen uitzien in Fig. 5.6.

De vergelijkende rechtheid van de plot laat zien dat voor de lage waardegebieden van VDS, de weerstand is in principe uniform. Zoals VDSstijgt en nadert een niveau dat bekend staat als VP in figuur 5.6, worden de uitputtingsgebieden groter zoals weergegeven in figuur 5.4.

Dit resulteert in een schijnbare verlaging van de kanaalbreedte. Het afgenomen geleidingspad leidt tot een toename van de weerstand, waardoor de curve van Fig. 5.6 ontstaat.

Hoe meer horizontaal de curve wordt, des te hoger is de weerstand, wat aangeeft dat de weerstand in het horizontale gebied richting 'oneindige' ohm gaat. Toen VDSneemt toe in een mate waarin het lijkt alsof de twee uitputtingsgebieden contact zouden kunnen maken, zoals weergegeven in figuur 5.7, geeft aanleiding tot een situatie die bekend staat als pinch-off.

Het bedrag waarmee VDSontwikkelt deze situatie wordt de afknijpen spanning en het wordt gesymboliseerd door VP.zoals weergegeven in Fig. 5.6. In het algemeen is het woord pinch-off misleidend omdat het de huidige I impliceertDwordt 'afgeknepen' en daalt tot 0 A. Zoals blijkt uit Fig. 5.6 lijkt dit in dit geval nauwelijks evident. ikDbehoudt een verzadigingsniveau dat wordt gekenmerkt als IDSSin Afb.5.6.

De waarheid is dat een heel klein kanaal nog steeds bestaat, met een stroom met een aanzienlijk hoge concentratie.

Het punt waarop de ID niet wordt afgegeven afknijpen en behoudt het verzadigingsniveau zoals aangegeven in Fig.5.6 wordt bevestigd met het volgende bewijs:

Omdat er geen afvoerstroom is, wordt de mogelijkheid van verschillende potentiaalniveaus door het n-kanaalmateriaal geëlimineerd voor het bepalen van de veranderende hoeveelheden tegenvoorspanning langs de p-n-overgang. Het eindresultaat is het verlies van de uitputtingsregio-distributie die werd geactiveerd afknijpen om te beginnen met.

Als we V verhogenDSboven VP., het gebied met nauw contact waar de twee uitputtingsgebieden elkaar zullen ontmoeten, in lengte toenemen langs het kanaal. Het ID-niveau blijft echter in wezen ongewijzigd.

Dus het moment VDSis hoger dan Vpverwerft de JFET de kenmerken van de huidige bron.

Zoals bewezen in figuur 5.8 wordt de stroom in een JFET bepaald op ID= IkDSS, maar spanning VDShoger dan VP wordt vastgesteld door de aangesloten belasting.

De selectie van IDSS-notatie is gebaseerd op het feit dat het de afvoer naar bron-stroom is met een kortgesloten verbinding over de poort naar de bron.

Nader onderzoek levert ons de volgende evaluatie op:

ikDSSis de hoogste afvoerstroom voor een JFET en wordt bepaald door de voorwaarden VGS= 0 V en VDS> | VP |.

Merk op dat in Fig.5.6 VGSis 0V voor het volledige stuk van de curve. In de volgende secties zullen we leren hoe de attributen van Fig 5.6 worden beïnvloed als het niveau van VGSis gevarieerd.

VGS <0V

De vluchtigheid die over de poort en de bron wordt toegepast, wordt aangeduid als de VGS, die verantwoordelijk is voor het besturen van de JFET-bewerkingen.

Als we het voorbeeld nemen van een BJT, net als de rondingen van ICversus VDITworden bepaald voor verschillende niveaus van IB., op dezelfde manier de rondingen van IDversus VDSvoor verschillende niveaus van VGSkan worden gemaakt voor een JFET-tegenhanger.

Hiervoor wordt de poortaansluiting ingesteld op een continu lager potentiaal onder het niveau van het bronpotentiaal.

Verwijzend naar figuur 5.9 hieronder, wordt een -1V toegepast over de gate / source-aansluitingen voor een gereduceerde VDSniveau.

Het doel van negatieve potentiële bias VGSis het ontwikkelen van uitputtingsregio's die lijken op de situatie van VGS= 0, maar bij aanzienlijk verminderde VDS

Dit zorgt ervoor dat de poort een verzadigingspunt bereikt met een lager niveau van VDSzoals aangegeven in Fig.5.10 (VGS= -1V).

Het corresponderende saturatieniveau voor IDblijkt te zijn verminderd en gaat eigenlijk gewoon verder met afnemen als VGSwordt negatiever gemaakt.

In Fig. 5.10 kun je duidelijk zien hoe de afknijpspanning blijft dalen met een parabolische vorm als VGSwordt steeds negatiever.

Eindelijk, toen VGS= -Vp, wordt het voldoende negatief om een verzadigingsniveau vast te stellen dat uiteindelijk 0 mA is. Op dit niveau staat de JFET volledig 'UIT'.

Het niveau van VGSwaardoor ikDom 0 mA te bereiken wordt gekenmerkt door VGS= VP., waarin VP.is een negatieve spanning voor n-kanaals apparaten en een positieve spanning voor p-kanaals JFET's.

Gewoonlijk vindt u de meeste JFET-gegevensbladen die worden weergegeven afknijpen spanning gespecificeerd als VGS (uit)in plaats van VP.

Het gebied aan de rechterkant van de pinch-off-locus in de bovenstaande afbeelding is de plaats die gewoonlijk wordt gebruikt in lineaire versterkers om een vervormingsvrij signaal te verkrijgen. Deze regio wordt over het algemeen genoemd gebied met constante stroom, verzadiging of lineaire versterking.

Spanningsgestuurde weerstand

Het gebied dat zich aan de linkerkant van de pinch-off locus in dezelfde figuur bevindt, wordt de ohmse regio of het spanningsgestuurde weerstandsgebied.

In dit gebied kan het apparaat in feite worden bediend als een variabele weerstand (bijvoorbeeld in automatische versterkingsregelingstoepassingen), waarbij de weerstand wordt geregeld via het aangelegde poort- / bronpotentiaal.

U kunt zien dat de helling van elk van de curven die ook de afvoer- / bronweerstand van de JFET voor V aangeeftDS

Naarmate we VGS hoger maken met een negatief potentieel, wordt de helling van elke curve steeds meer horizontaal, met proportioneel toenemende weerstandsniveaus.

We zijn in staat om een goede eerste benadering te krijgen van het niveau van de weerstand met betrekking tot de VGS-spanning, door middel van de volgende vergelijking.

p-Channel JFET werken

De interne lay-out en constructie van een p-kanaal JFET is precies identiek aan de n-kanaal-tegenhanger, behalve dat de p- en n-type materiaalgebieden zijn omgekeerd, zoals hieronder getoond:

De richtingen van de stroom kunnen ook als omgekeerd worden gezien, samen met de feitelijke polariteiten van spanning VGS en VDS. In het geval van een p-kanaal JFET, wordt het kanaal beperkt als reactie op een toenemend positief potentieel over de poort / bron.

De notatie met een dubbel subscript voor de VDSzal aanleiding geven tot een negatieve spanning voor V.DS, zoals getoond op de kenmerken van Fig.5.12. Hier kun je I vindenDSSbij 6 mA, terwijl een afknijpspanning op VGS= + 6V.

Raak alsjeblieft niet verbaasd vanwege de aanwezigheid van het minteken voor de VDSHet geeft eenvoudig aan dat de bron een hoger potentieel heeft dan de afvoer.

Je kunt zien dat de curven voor hoge VDSniveaus stijgen abrupt tot waarden die er onbeperkt uitzien. De aangegeven stijging die verticaal is, symboliseert een storing, wat betekent dat de stroom door het kanaalapparaat op dit moment volledig wordt gecontroleerd door de externe schakelingen.

Hoewel dit niet duidelijk is in figuur 5.10 voor een n-kanaals apparaat, kan het een mogelijkheid zijn onder voldoende hoge spanning.

Dit gebied kan worden geëlimineerd als de VDS (max.)wordt vermeld op het gegevensblad van het apparaat en het apparaat is zo geconfigureerd dat de werkelijke VDSwaarde is lager dan deze genoteerde waarde voor elke VGS

Een paar: 5 beste 40 watt versterkercircuits onderzocht Volgende: 2N3055 Datasheet, Pinout, Application Circuits