Het ontwerpproces van digitale hardware is de afgelopen jaren sterk veranderd. Kleine digitale schakelingen kunnen dus worden geïmplementeerd door PAL's en PLA's te gebruiken. Elk apparaat wordt gebruikt om verschillende circuits te implementeren die niet meer nodig hebben dan het aantal i / ps, o / ps en producttermen die in de specifieke chip worden aangeboden. Deze chips zijn ontoereikend voor redelijk bescheiden afmetingen, en ondersteunen normaal gesproken een gemeenschappelijk aantal in- en uitgangen van niet meer dan 32. Voor het ontwerpen van deze circuits die meer in- en uitgangen nodig hebben, kunnen ofwel talrijke PLA's / PAL's worden gebruikt of anders een meer stijlvol type. van de chip kan een CPLD (complex programmeerbaar logisch apparaat) worden genoemd. Een CPLD-chip bevat verschillende circuitblokken op een enkele chip met interne bedradingsbronnen om de circuitblokken aan te sluiten. Elk circuitblok is vergelijkbaar met een PLA of een PAL.

Wat is een complex programmeerbaar logisch apparaat?

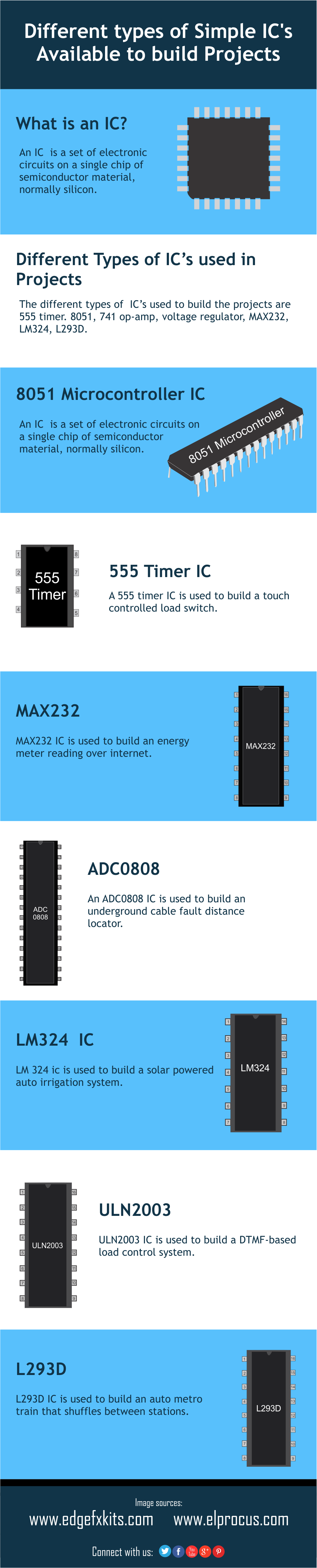

Het acroniem van de CPLD is 'Complexe programmeerbare logische apparaten', het is een soort geïntegreerde schakeling die applicatieontwerpers ontwerpen om digitale hardware zoals mobiele telefoons te implementeren. Deze kunnen bewust hogere ontwerpen aan dan SPLD's (eenvoudige programmeerbare logische apparaten), maar bieden minder logica dan FPGA's ( veldprogrammeerbare gate-arrays CPPLD's bevatten talrijke logische blokken, elk van de blokken bevat 8-16 macrocellen. Omdat elk logisch blok een specifieke functie uitvoert, zijn alle macrocellen in een logisch blok volledig verbonden. Afhankelijk van het gebruik zijn deze blokken al dan niet met elkaar verbonden.

Complex programmeerbaar logisch apparaat

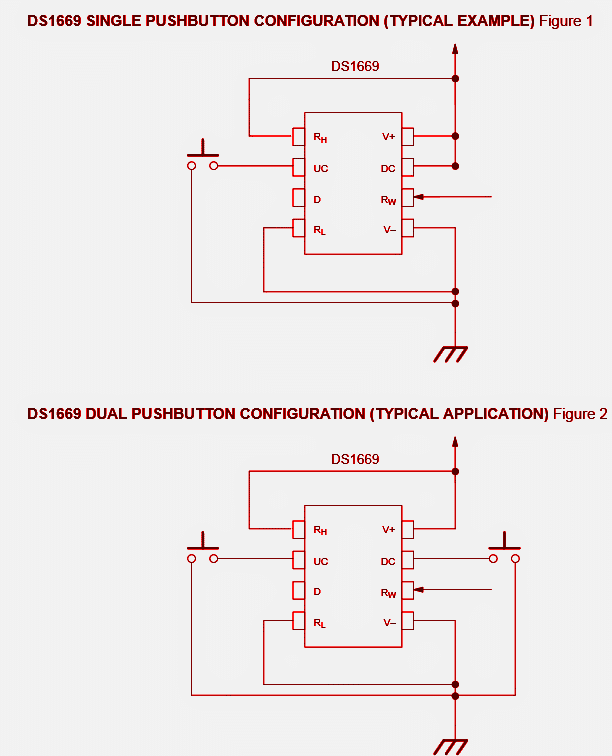

De meeste CPLD's (complexe programmeerbare logische apparaten) hebben macrocellen met een som van logische functies en een keuzevak FF (flip-flop) Afhankelijk van de chip ondersteunt de combinatorische logische functie 4 tot 16 producttermen inclusief fan-in. CPLD's verschillen ook in termen van schuifregisters en logische poorten. Om deze reden kunnen CPLD's met een groot aantal logische poorten worden gebruikt in plaats van FPGA's. Een andere CPLD-specificatie geeft het aantal producttermen aan dat een macrocel kan bereiken. Producttermen zijn het product van digitale signalen die een specifieke logische functie uitvoeren.

CPLD's zijn beschikbaar in verschillende IC-pakketvormen en logicafamilies. CPLD's verschillen ook in termen van voedingsspanning, bedrijfsstroom, stand-bystroom en vermogensdissipatie. Bovendien zijn deze verkrijgbaar met verschillende hoeveelheden geheugen en verschillende soorten geheugenondersteuning. Meestal wordt geheugen uitgedrukt in bits / megabits. Geheugenondersteuning bestaat uit ROM, RAM en dual-port RAM. Het bevat ook CAM (content adresseerbaar geheugen) evenals FIFO-geheugen (first-in, first-out) en LIFO-geheugen (last-in, last-out).

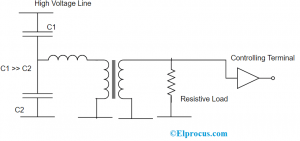

Architectuur van complex programmeerbaar logisch apparaat

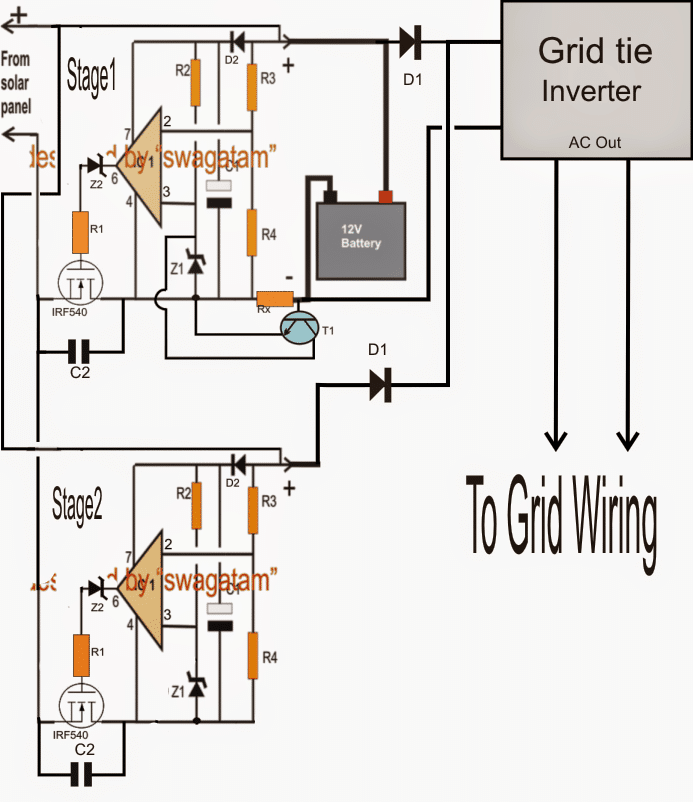

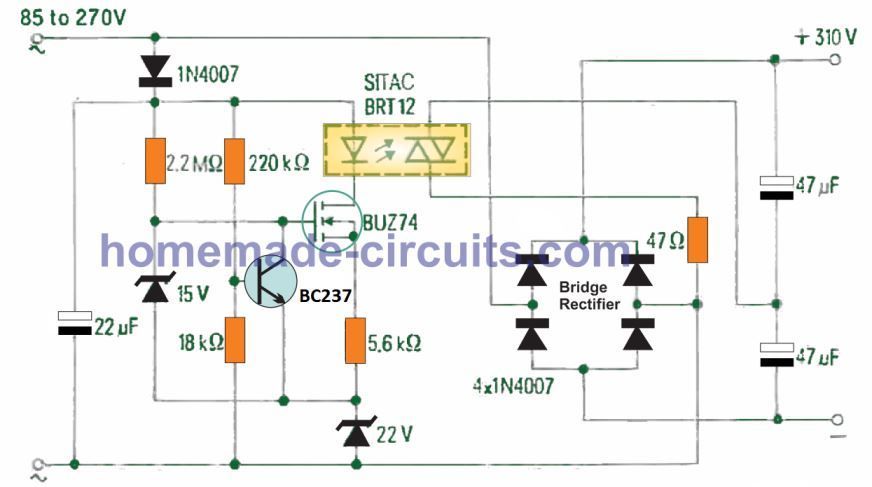

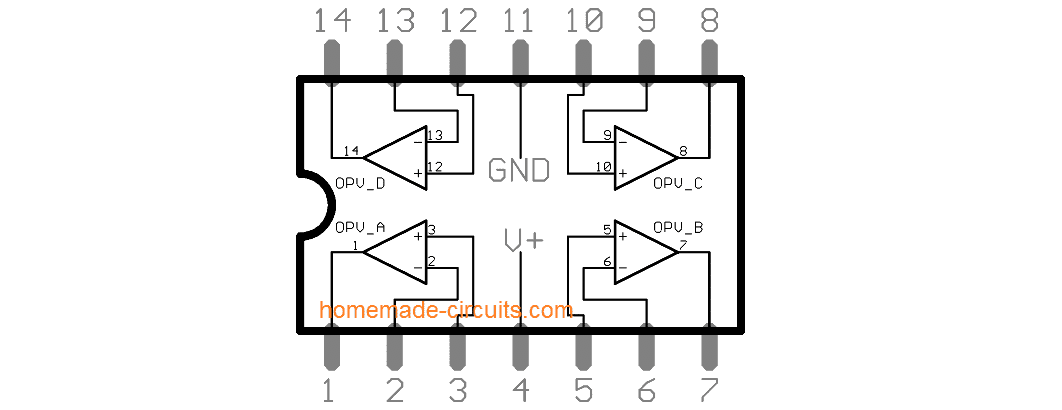

Een complex programmeerbaar logisch apparaat bestaat uit een groep programmeerbare FB's (functionele blokken). De in- en uitgangen van deze functionele blokken zijn met elkaar verbonden door middel van een GIM (global interconnection matrix). Deze interconnectiematrix is herconfigureerbaar, zodat we de contacten tussen de functionele blokken kunnen wijzigen. Er zullen enkele invoer- en uitvoerblokken zijn waarmee we CPLD kunnen verenigen met de externe wereld. De architectuur van CPLD wordt hieronder weergegeven.

Over het algemeen ziet de programmeerbare FB eruit als de array van logische poorten , waar een reeks EN-poorten kan worden geprogrammeerd en OF-poorten stabiel zijn. Maar elke fabrikant heeft zijn manier van denken om het functionele blok te ontwerpen. Een weergegeven o / p kan worden gevonden door de feedbacksignalen te bedienen die worden verkregen van de OF-poortuitgangen.

CPLD-architectuur

Bij CPLD-programmering wordt het ontwerp eerst gecodeerd in Verilog- of VHDL-taal zodra de code is (gesimuleerd en gesynthetiseerd. Tijdens de synthese wordt het CPLD-model (doelapparaat) met de hand geselecteerd en wordt een op technologie gebaseerde mappingnetlijst gemaakt. Deze lijst kan worden afgesloten -aanpassing aan de echte CPLD-architectuur met behulp van een plaats- en routeproces, meestal bereikt door de plaats-en-routesoftware van het bedrijfseigen bedrijf van CPLD. Vervolgens voert de operator enkele bevestigingsprocessen uit. Als alles goed is, gebruikt hij de CPLD, anders hij zal het herschikken.

Architectuurkwesties van CPLD

Bij het overwegen van een complex programmeerbaar logisch apparaat voor gebruik bij het ontwerp, zijn er enkele volgende architectuurkwesties waarmee rekening kan worden gehouden

- De programmeertechnologie

- De functieblok-mogelijkheid

- De I / O-mogelijkheid

Enkele van de CPLD-families van verschillende retailers omvatten

- Altera MAX 7000 en MAX 9000 families

- Atmel ATF- en ATV-families

- Lattice isp LSI-familie

- Lattice (Vantis) MACH-familie

- Xilinx XC9500-familie

Families van CPLD

Toepassingen van CPLD

De toepassingen van CPLD's omvatten de volgende

- Complexe programmeerbare logische apparaten zijn ideaal voor hoogwaardige, kritische besturingstoepassingen.

- CPLD kan in digitale ontwerpen worden gebruikt om de functies van bootloader uit te voeren

- CPLD wordt gebruikt voor het laden van de configuratiegegevens van een veldprogrammeerbare gate-array uit niet-vluchtig geheugen.

- Over het algemeen worden deze gebruikt in kleine ontwerptoepassingen zoals adresdecodering

- CPLD's worden vaak gebruikt in veel toepassingen, zoals in kostengevoelige, op batterijen werkende draagbare apparaten vanwege de geringe omvang en het lage energieverbruik.

Dit gaat dus allemaal over de complexe architectuur van programmeerbare logische apparaten en de toepassingen ervan. We hopen dat u dit concept beter begrijpt. Verder kunnen eventuele vragen over dit concept of om elektrische en elektronische projecten uit te voeren , geef alstublieft uw waardevolle suggesties door te reageren in de commentaarsectie hieronder. Hier is een vraag voor jou, wat is het verschil tussen CPLD en FPGA?

Fotocredits:

- CPLD wikimedia

- Architectuur van CPLD slidesharecdn