De MOS-transistor is het meest fundamentele element in het grootschalige ontwerp van geïntegreerde schakelingen. Deze transistors worden over het algemeen ingedeeld in twee typen PMOS en NMOS. De combinatie van NMOS- en PMOS-transistors staat bekend als a CMOS-transistor . Het verschil logische poorten en andere digitale logische apparaten die zijn geïmplementeerd, moeten PMOS-logica hebben. Deze technologie is goedkoop en heeft een goede weerstand tegen interferentie. Dit artikel bespreekt een van de typen MOS-transistors zoals een PMOS-transistor.

Wat is PMOS-transistor?

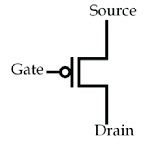

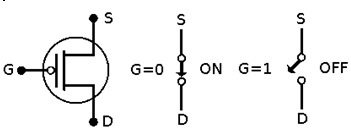

De PMOS-transistor of P-kanaal metaaloxide-halfgeleider is een soort transistor waarbij de p-type doteermiddelen worden gebruikt in het kanaal- of poortgebied. Deze transistor is precies het omgekeerde van de NMOS Transistor. Deze transistors hebben drie hoofdterminals; de bron, de poort en de afvoer waar de bron van de transistor is ontworpen met een p-type substraat en de afvoeraansluiting is ontworpen met een n-type substraat. In deze transistor zijn de ladingdragers als gaten verantwoordelijk voor de stroomgeleiding. De PMOS-transistorsymbolen worden hieronder weergegeven.

Hoe werkt PMOS-transistor?

De werking van de p-type transistor is precies het tegenovergestelde van de n-type transistor. Deze transistor zal een open circuit vormen wanneer hij een niet te verwaarlozen spanning krijgt, wat betekent dat er geen stroom van elektriciteit is van de poort (G) aansluiting naar de bron (S). Evenzo vormt deze transistor een gesloten circuit wanneer hij een spanning van ongeveer 0 volt krijgt, wat betekent dat de stroom van de gate (G)-terminal naar de drain (D) vloeit.

Deze bubbel wordt ook wel een inversiebubbel genoemd. De belangrijkste functie van deze cirkel is dus het inverteren van de ingangsspanningswaarde. Als de poortterminal een 1-spanning levert, zal deze omvormer deze in nul veranderen en het circuit dienovereenkomstig laten werken. De functie van de PMOS-transistor en de NMOS-transistor is dus precies het tegenovergestelde. Zodra we ze samenvoegen tot een enkel MOS-circuit, wordt het een CMOS-circuit (complementary metal-oxide semiconductor).

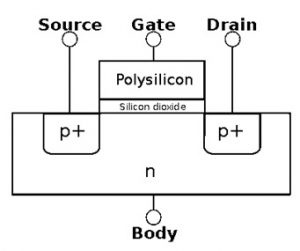

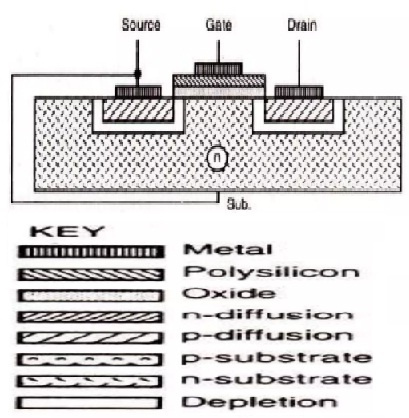

Dwarsdoorsnede van PMOS-transistor

De dwarsdoorsnede van de PMOS-transistor wordt hieronder weergegeven. Een pMOS-transistor is gebouwd met een n-type lichaam met twee p-type halfgeleidergebieden die grenzen aan de poort. Deze transistor heeft een controlerende poort zoals getoond in het diagram die de elektronenstroom regelt tussen de twee terminals zoals source & drain. In de pMOS-transistor wordt het lichaam op +ve spanning gehouden. Zodra de gate-aansluiting positief is, zijn de source- en drain-aansluitingen in tegengestelde richting voorgespannen. Zodra dit gebeurt, is er geen stroom meer, dus wordt de transistor uitgeschakeld.

Zodra de voedingsspanning op de gate-aansluiting is verlaagd, zullen positieve ladingsdragers worden aangetrokken naar de onderkant van de Si-SiO2-interface. Telkens wanneer de spanning voldoende laag wordt, wordt het kanaal omgekeerd en ontstaat er een geleidend pad van de source-terminal naar de drain door de stroom door te laten.

Wanneer deze transistors met digitale logica te maken hebben, hebben ze meestal slechts twee verschillende waarden, zoals 1 en 0 (AAN en UIT). De positieve spanning van de transistor staat bekend als VDD, wat de logische hoge (1) waarde binnen digitale circuits vertegenwoordigt. De VDD-spanning komt binnen TTL-logica waren over het algemeen rond de 5V. Op dit moment zijn transistors niet bestand tegen zulke hoge spanningen, omdat ze typisch variëren van 1,5V - 3,3V. De laagspanning wordt vaak GND of VSS genoemd. VSS betekent dus de logische '0' en is ook normaal ingesteld op 0V.

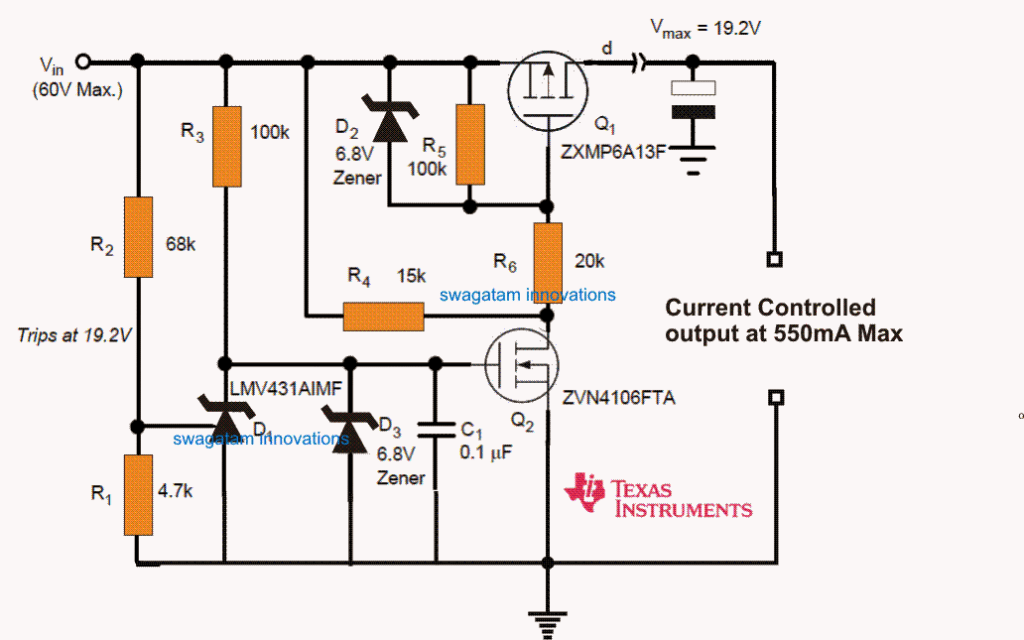

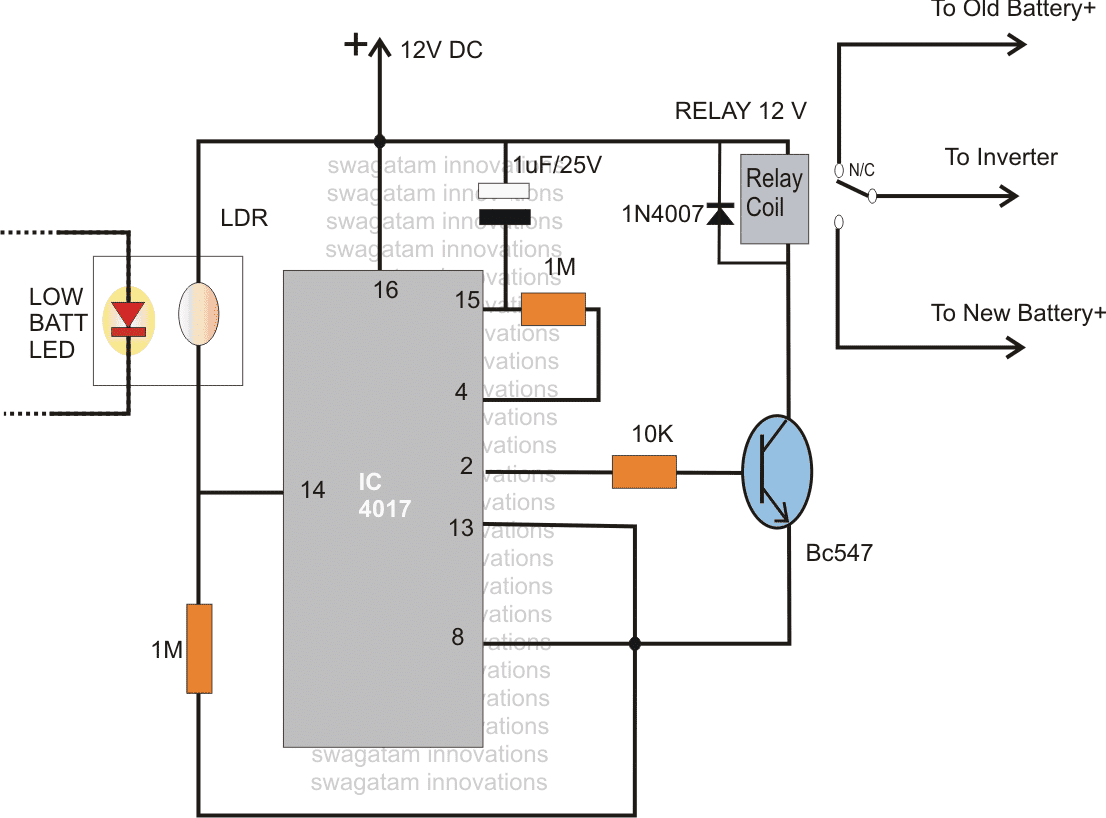

PMOS-transistorcircuit

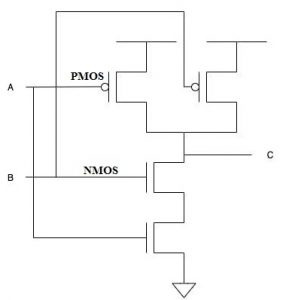

Het ontwerp van de NAND-poort met behulp van de PMOS-transistor en de NMOS-transistor wordt hieronder weergegeven. Over het algemeen is een NAND-poort in digitale elektronica een logische poort die ook wel een NIET-EN-poort wordt genoemd. De uitvoer van deze poort is alleen laag (0) als de twee ingangen hoog zijn (1) en de uitvoer is een aanvulling op een EN-poort. Als een van de twee ingangen LAAG (0) is, geeft dit hoge uitgangsresultaten.

Als in het onderstaande logische circuit de ingang A 0 is en B 0, dan zal een ingang van pMOS '1' produceren en zal een ingang van nMOS '0' produceren. Deze logische poort genereert dus een logische '1' omdat deze via een gesloten circuit met de bron is verbonden en via een open circuit is losgekoppeld van de GND.

Wanneer A '0' is en B' '1' is, genereert een invoer van pMOS een '1' en genereert een invoer van NMOS een '0'. Deze poort zal dus een logische poort produceren omdat deze via een gesloten circuit met de bron is verbonden en via een open circuit is losgekoppeld van de GND. Wanneer A '1' is en B '0' is, genereert de 'B'-invoer van pMOS een hoge uitvoer (1) en 'B'-invoer van NMOS genereert een uitvoer als laag (0). Deze logische poort zal dus een logische 1 genereren omdat deze via een gesloten circuit met de bron is verbonden en door een open circuit is losgekoppeld van de GND.

Wanneer A '1' is en B '1', dan zal een invoer van 'pMOS een nul produceren en een invoer van nMOS zal een '1' genereren. Daarom moeten we ook de B-invoer van pMOS & nMOS verifiëren. De B-ingang van pMOS genereert een '0' en de B-ingang van nMOS genereert een '1'. Deze logische poort genereert dus een logische '0' omdat deze is losgekoppeld van de bron door een open circuit en is verbonden met de GND via een gesloten circuit.

Waarheidstabel

De waarheidstabel van het bovenstaande logische circuit wordt hieronder gegeven.

|

EEN |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

De drempelspanning van de PMOS-transistor is normaal gesproken de 'Vgs' die nodig is om het kanaal te creëren dat bekend staat als kanaalinversie. In een PMOS-transistor zijn het substraat en de bronterminals eenvoudigweg verbonden met 'Vdd'. Als we beginnen met het verlagen van de spanning door te verwijzen naar de bronterminal bij poortterminal van Vdd naar een punt waar u de kanaalinversie opmerkt, op deze positie als u analyseert dat Vgs & bron op het hoge potentieel zijn, dan krijgt u een negatieve waarde. De PMOS-transistor heeft dus een negatieve Vth-waarde.

PMOS-fabricageproces

De stappen die betrokken zijn bij de fabricage van PMOS-transistors worden hieronder besproken.

Stap 1:

Een dunne siliciumwafellaag wordt veranderd in N-type materiaal door simpelweg fosformateriaal te doteren.

Stap 2:

Op een compleet p-type substraat wordt een dikke Siliciumdioxide (Sio2) laag gegroeid.

Stap 3:

Nu wordt het oppervlak bedekt met een fotoresist over de dikke laag siliciumdioxide.

Stap 4:

Daarna wordt deze laag eenvoudigweg blootgesteld aan UV-licht via een masker dat samen met transistorkanalen de gebieden definieert waarin diffusie moet plaatsvinden.

Stap5:

Deze gebieden worden wederzijds weggeëtst met het onderliggende siliciumdioxide, zodat het oppervlak van de wafel wordt blootgelegd binnen het venster dat wordt bepaald door het masker.

Stap6:

De resterende fotoresist wordt losgemaakt en er wordt een dunne Sio2-laag gegroeid van typisch 0,1 micrometer over het gehele oppervlak van de chip. Daarna wordt er polysilicium overheen geplaatst om de structuur van de poort te vormen. Een fotoresist wordt over de hele polysiliciumlaag geplaatst en belicht UV-licht door het masker2.

Stap7:

Diffusies worden bereikt door waferverwarming tot maximale temperatuur en doorgang van gas met gewenste p-type onzuiverheden zoals boor.

Stap8:

Een siliciumdioxide met een dikte van 1 micrometer wordt gekweekt en er wordt fotoresistmateriaal op afgezet. Belicht het ultraviolette licht met mask3 op de voorkeursgebieden van de poort, bron en afvoer die zijn geëtst om de contactsneden te maken.

Stap9:

Nu wordt een metaal of aluminium afgezet over het oppervlak met een dikte van 1 micrometer. Opnieuw wordt een fotolakmateriaal over het hele metaal gegroeid en wordt het UV-licht door masker4 belicht dat wordt geëtst om het vereiste verbindingsontwerp te vormen. De uiteindelijke PMOS-structuur wordt hieronder weergegeven.

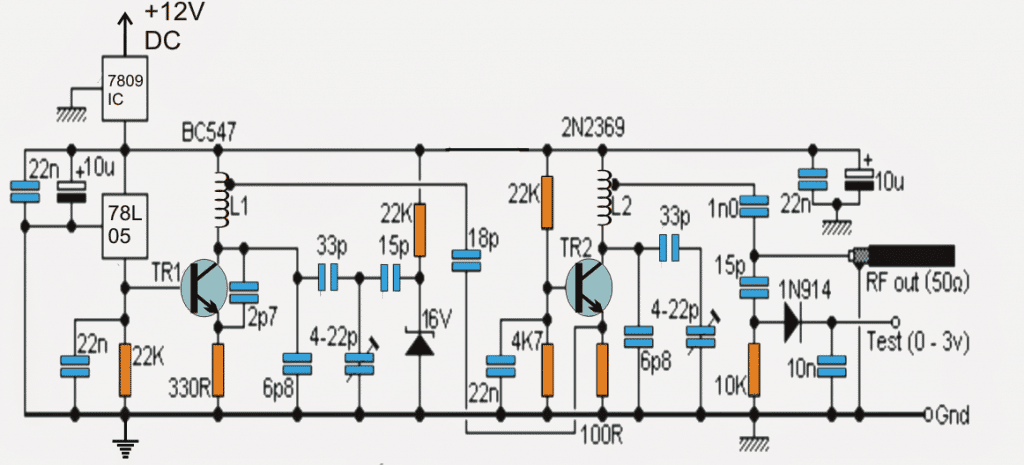

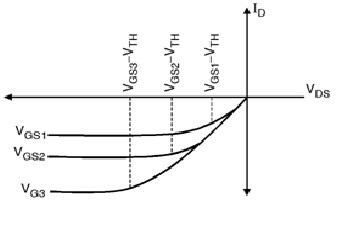

PMOS-transistorkenmerken

De kenmerken van de PMOS-transistor I-V worden hieronder weergegeven. Deze karakteristieken zijn verdeeld in twee regio's om de relatie tussen de drain-to-source-stroom (IDS) en de eindspanningen ervan te verkrijgen, zoals lineaire en verzadigingsgebieden.

In een voeringgebied zal de IDS lineair toenemen wanneer de VDS (afvoer naar bronspanning) wordt verhoogd, terwijl in het verzadigingsgebied de IDS stabiel is en onafhankelijk is van VDS. De belangrijkste relatie tussen de ISD (source-to-drain-stroom) en zijn klemspanningen wordt afgeleid door een vergelijkbare procedure van de NMOS-transistor. In dit geval is de enige verandering dat de ladingsdragers die aanwezig zijn in de inversielaag gewoon gaten zijn. Wanneer de gaten van bron naar afvoer gaan, is de stroomstroom ook hetzelfde.

Het negatieve teken verschijnt dus binnen de huidige vergelijking. Bovendien zijn alle toegepaste voorspanningen op de aansluitingen van het apparaat negatief. Dus de ID - VDS-kenmerken van de PMOS-transistor worden hieronder weergegeven.

De afvoerstroomvergelijking voor PMOS-transistor in het lineaire gebied wordt gegeven als:

ID = – mp Cox

Evenzo wordt de afvoerstroomvergelijking voor PMOS-transistor in het verzadigingsgebied gegeven als:

ID = – mp Cox (VSG – | VTH |p )^2

Waarbij ‘mp’ de mobiliteit van de hole is & ‘|VTH| p' is de drempelspanning van de PMOS-transistor.

In de bovenstaande vergelijking geeft het negatieve teken aan dat de ID( drain stroom ) stroomt van de afvoer (D) naar de bron (S) terwijl gaten in de tegenovergestelde richting stromen. Wanneer de mobiliteit van het gat laag is in vergelijking met de elektronenmobiliteit, lijden PMOS-transistors onder het vermogen van de lage stroomaandrijving.

Dit gaat dus allemaal over een overzicht van PMOS-transistor of p-type mos-transistor - fabricage, circuit en zijn werking. PMOS transistors zijn ontworpen met een p-bron, een n-substraat & drain. De ladingsdragers van PMOS zijn gaten. Deze transistor geleidt zodra een lage spanning wordt toegepast op de poortaansluiting. Op PMOS gebaseerde apparaten zijn minder gevoelig voor interferentie in vergelijking met NMOS-apparaten. Deze transistors kunnen worden gebruikt als spanningsgestuurde weerstanden, actieve belastingen, stroomspiegels, trans-impedantieversterkers en ook in schakelaars en spanningsversterkers. Hier is een vraag voor u, wat is een NMOS-transistor?