De metaaloxide-halfgeleidertransistor of MOS-transistor is een basisbouwsteen in logische chips, processors en moderne digitale geheugens. Het is een apparaat met een meerderheidsdrager, waarbij de stroom in een geleidend kanaal tussen de bron en de afvoer wordt gemoduleerd door een aangelegde spanning op de poort. Deze MOS-transistor speelt een sleutelrol in verschillende analoge en mixed-signal IC's. Deze transistor is behoorlijk aanpasbaar, dus functioneert als een versterker, een schakelaar of een weerstand . niet transistoren zijn ingedeeld in twee typen PMOS & NMOS. Dus, dit artikel bespreekt een overzicht van NMOS-transistor - fabricage, circuit & werken.

Wat is een NMOS-transistor?

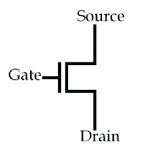

Een NMOS-transistor (n-channel metal-oxide semiconductor) is een type transistor waarbij doteermiddelen van het n-type worden gebruikt in het poortgebied. Een positieve (+ve) spanning op de gate-aansluiting zet het apparaat aan. Deze transistor wordt voornamelijk gebruikt in CMOS (complementaire metaaloxide halfgeleider) ontwerp en ook in logica- en geheugenchips. In vergelijking met de PMOS-transistor is deze transistor veel sneller, waardoor er meer transistors op één chip kunnen worden geplaatst. Het NMOS-transistorsymbool wordt hieronder weergegeven.

Hoe werkt NMOS-transistor?

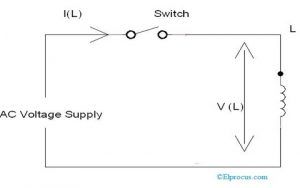

De werking van de NMOS transistor is; wanneer de NMOS-transistor een niet te verwaarlozen spanning ontvangt, vormt deze een gesloten circuit, wat betekent dat de verbinding van de source-terminal naar de drain werkt als een draad. Dus de stroom vloeit van de poortterminal naar de bron. Evenzo, wanneer deze transistor een spanning van ongeveer 0 V ontvangt, vormt deze een open circuit, wat betekent dat de verbinding van de source-terminal naar de drain wordt verbroken, zodat er stroom van de gate-terminal naar de drain vloeit.

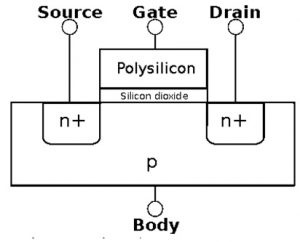

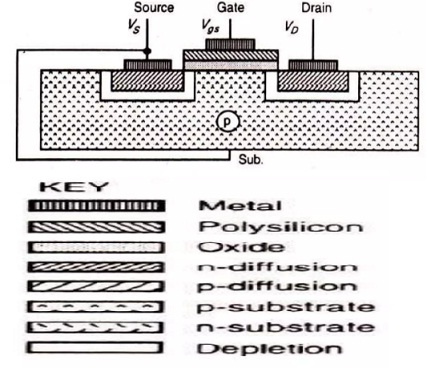

Dwarsdoorsnede van NMOS-transistor

Over het algemeen wordt een NMOS-transistor eenvoudigweg gebouwd met een p-type lichaam door twee n-type halfgeleidergebieden die grenzen aan de poort die bekend staat als de bron en de afvoer. Deze transistor heeft een controlerende poort die de elektronenstroom tussen de bron- en afvoeraansluitingen regelt.

Aangezien het lichaam van de transistor in deze transistor is geaard, zijn de PN-overgangen van de source & drain naar het lichaam in tegengestelde richting voorgespannen. Als de spanning op de gate-terminal wordt verhoogd, zal een elektrisch veld beginnen toe te nemen en vrije elektronen naar de basis van de Si-SiO2-interface trekken.

Zodra de spanning hoog genoeg is, zullen elektronen alle gaten vullen en een dun gebied onder de poort, bekend als het kanaal, zal worden omgekeerd om te presteren als een n-type halfgeleider. Dit creëert een geleidende baan van de source-terminal naar de drain door de stroom door te laten, zodat de transistor wordt ingeschakeld. Als de gate-aansluiting geaard is, vloeit er geen stroom in de sperpuntovergang, zodat de transistor wordt uitgeschakeld.

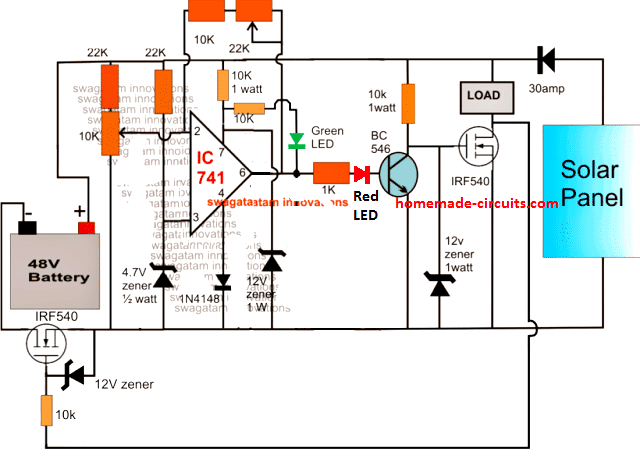

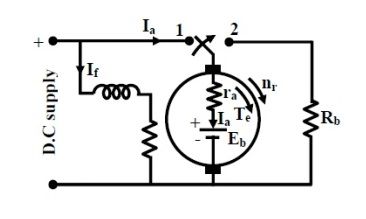

NMOS-transistorcircuit

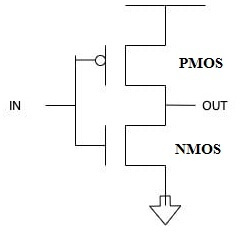

Het NOT-poortontwerp met PMOS- en NMOS-transistors wordt hieronder weergegeven. Om een NOT-poort te ontwerpen, moeten we pMOS- en nMOS-transistors combineren door een pMOS-transistor aan te sluiten op de bron en een nMOS-transistor op aarde. Het circuit wordt dus ons eerste voorbeeld van een CMOS-transistor.

De NOT-poort is een type logische poort die een geïnverteerde invoer als uitvoer genereert. Deze poort wordt ook wel een inverter genoemd. Als de invoer '0' is, is de omgekeerde uitvoer '1'.

Als de invoer nul is, gaat deze naar de pMOS-transistor bovenaan en omlaag naar de nMOS-transistor onderaan. Zodra de invoerwaarde '0' de pMOS-transistor bereikt, wordt deze omgezet in '1'. dus wordt de verbinding met de bron gestopt. Dit zal dus een logische '1'-waarde genereren als de verbinding naar de afvoer (GND) ook gesloten is. We weten dat de nMOS-transistor de invoerwaarde niet zal omkeren, dus neemt hij de nulwaarde zoals die is en maakt hij een open circuit naar de afvoer. Er wordt dus een logische waarde voor de poort gegenereerd.

Evenzo, als de ingangswaarde '1' is, wordt deze waarde naar beide transistors in het bovenstaande circuit gestuurd. Zodra de '1'-waarde de pMOS-transistor ontvangt, wordt deze geïnverteerd naar een 'o'. hierdoor is de verbinding naar de bron open. Zodra de nMOS-transistor de '1-waarde ontvangt, wordt deze niet omgekeerd. dus de invoerwaarde blijft één. Zodra één waarde is ontvangen door de nMOS-transistor, wordt de verbinding naar de GND gesloten. Het genereert dus een logische '0' als uitvoer.

Fabricageproces

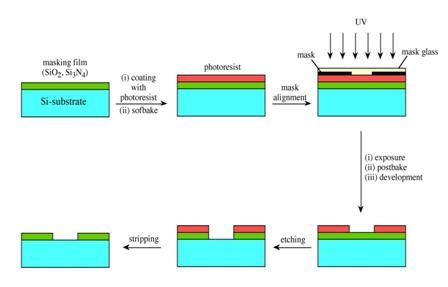

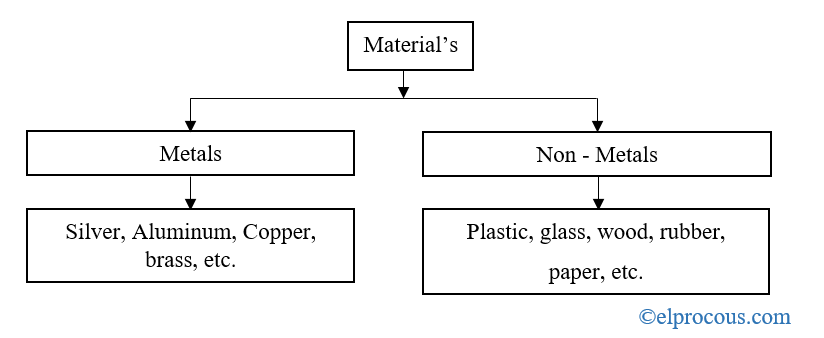

Er zijn veel stappen betrokken bij het fabricageproces van de NMOS-transistor. Hetzelfde proces kan worden gebruikt voor PMOS- en CMOS-transistors. Het meest gebruikte materiaal in deze fabricage is polysilicium of metaal. De stapsgewijze fabricageprocesstappen van de NMOS-transistor worden hieronder besproken.

Stap 1:

Een dunne silicium waferlaag wordt veranderd in P-type materiaal door simpelweg te doteren met boormateriaal.

Stap 2:

Op een volledig p-type substraat wordt een dikke Sio2-laag gekweekt

Stap 3:

Nu wordt het oppervlak gecoat door een fotoresist op de dikke Sio2-laag.

Stap 4:

Daarna wordt deze laag blootgesteld aan UV-licht met een masker dat de gebieden beschrijft waarin diffusie moet plaatsvinden samen met transistorkanalen.

Stap5:

Deze gebieden worden wederzijds weggeëtst met de onderliggende Sio2 zodat het oppervlak van de wafer zichtbaar wordt binnen het venster dat door het masker wordt gedefinieerd.

Stap6:

De resterende fotoresist wordt gescheiden en een dunne Sio2-laag wordt 0,1 micrometer gegroeid, typisch over het hele oppervlak van de chip. Vervolgens wordt hierop polysilicium aangebracht om de poortstructuur te vormen. Een fotoresist wordt op de volledige polysiliciumlaag geplaatst en belicht ultraviolet licht door het hele masker2.

Stap7:

Door de wafel tot de maximale temperatuur te verwarmen, worden diffusies bereikt en wordt gas doorgelaten met gewenste n-type onzuiverheden zoals fosfor.

Stap8:

Een dikte van één micrometer siliciumdioxide wordt overal gegroeid en er wordt fotoresistmateriaal op geplaatst. Belicht het ultraviolette licht (UV) via mask3 op de voorkeursgebieden van poort, bron- en afvoergebieden zijn geëtst om de contactsneden te maken.

Stap9:

Nu wordt een metaalachtig aluminium over het oppervlak van één micrometer breed geplaatst. Opnieuw wordt een fotoresistmateriaal over het hele metaal gegroeid en blootgesteld aan UV-licht door mask4, wat een geëtste vorm is van het verplichte verbindingsontwerp. De uiteindelijke NMOS-structuur wordt hieronder weergegeven.

PMOS versus NMOS-transistor

Het verschil tussen PMOS- en NMOS-transistors wordt hieronder besproken.

| PMOS-transistor | NMOS-transistor |

| PMOS-transistor staat voor P-kanaal metaaloxide-halfgeleidertransistor. | NMOS-transistor staat voor N-kanaal metaaloxide-halfgeleidertransistor. |

| De bron en de afvoer in PMOS-transistors zijn eenvoudig gemaakt met halfgeleiders van het n-type | De bron en de afvoer in de NMOS-transistor zijn eenvoudig gemaakt met halfgeleiders van het p-type. |

| Het substraat van deze transistor is gemaakt met een n-type halfgeleider | Het substraat van deze transistor is gemaakt met de p-type halfgeleider |

| De meeste ladingsdragers in PMOS zijn gaten. | De meeste ladingsdragers in NMOS zijn elektronen. |

| In vergelijking met NMOS zijn PMOS-apparaten niet kleiner. | NMOS-apparaten zijn vrij kleiner in vergelijking met PMOS-apparaten. |

| PMOS-apparaten kunnen niet sneller worden geschakeld in vergelijking met NMOS-apparaten. | In vergelijking met PMOS-apparaten kunnen NMOS-apparaten sneller worden geschakeld. |

| PMOS-transistor zal geleiden zodra een lage spanning aan de poort wordt geleverd. | NMOS-transistor zal geleiden zodra een hoge spanning aan de poort wordt geleverd. |

| Deze zijn beter bestand tegen lawaai. | In vergelijking met PMOS zijn deze niet immuun voor ruis. |

| De drempelspanning (Vth) van deze transistor is een negatieve grootheid. | De drempelspanning (Vth) van deze transistor is een positieve grootheid. |

Eigenschappen

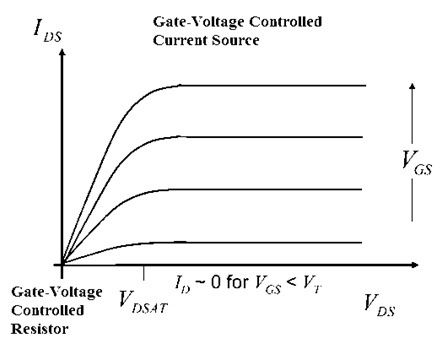

De IV-karakteristieken van de NMOS-transistor worden hieronder getoond. De spanning tussen de poort en de bronterminals 'V GS ’ & ook tussen de source & drain ‘V DS '. Dus de bochten tussen I DS en V DS worden bereikt door simpelweg de aansluiting van de bron te aarden, een initiële VGS-waarde in te stellen en V te vegen DS van '0' tot de hoogste gelijkspanningswaarde gegeven door de V dd bij het stappen van de V GS waarde van ‘0’ tot V dd . Dus voor extreem lage V GS , de ik DS zijn extreem klein en zullen een lineaire trend hebben. Wanneer de V GS waarde hoog wordt, dan I DS verbetert en heeft de onderstaande afhankelijkheid van V GS & IN DS ;

Als V GS is kleiner dan of gelijk aan V E , dan is de transistor UIT en presteert hij als een open circuit.

Als V GS groter is dan V E , dan zijn er twee bedrijfsmodi.

Als V DS is kleiner dan V GS - IN E , dan werkt de transistor in de lineaire modus en presteert als een weerstand (R AAN ).

IDS = u eff C os W/L [(V GS - IN E )IN DS – ½ V DS ^2]

Waar,

‘µeff’ is de effectieve mobiliteit van de ladingsdrager.

'COX' is de capaciteit van poortoxide voor elke oppervlakte-eenheid.

W & L zijn dienovereenkomstig de breedte en lengte van het kanaal. De R AAN waarde wordt eenvoudig geregeld door de spanning van de poort volgt als;

R AAN = 1 in n C os W/L [(V GS - IN E )IN DS – ½ V DS ^2]

Als VDS groter is dan of gelijk is aan V GS - IN E , dan werkt de transistor binnen de verzadigingsmodus

l DS = jij n C os W/L [(V GS - IN E )^2 (1+λ V DS ]

In deze regio, toen ik DS hoger is, dan is de stroom minimaal afhankelijk van de V DS waarde, maar de hoogste waarde wordt eenvoudig geregeld via VGS. De kanaallengtemodulatie 'λ' verklaart de toename binnen IDS door een toename binnen VDS in transistors, vanwege afknijpen. Deze afknijping vindt plaats zodra zowel V DS en V GS beslissen over het elektrische veldpatroon dichtbij het afvoergebied, waardoor de richting van de natuurlijke toevoerladingsdragers verandert. Dit effect vermindert de lengte van het efficiënte kanaal en verhoogt I DS . Idealiter is 'λ' gelijk aan '0' zodat I DS is volledig onafhankelijk van de V DS waarde binnen het verzadigingsgebied.

Hier gaat het dus allemaal om een overzicht van een NMOS transistor - fabricage en circuit met werking. NMOS-transistor speelt een sleutelrol bij het implementeren van logische poorten en andere verschillende digitale circuits. Dit is een micro-elektronische schakeling die voornamelijk wordt gebruikt bij het ontwerpen van logische circuits, geheugenchips en in CMOS-ontwerp. De meest populaire toepassingen van NMOS-transistors zijn schakelaars en spanningsversterkers. Hier is een vraag voor u, wat is een PMOS-transistor?