In dit artikel wordt het generatie van pulsbreedtemodulatie signalen met variabele duty-cycle op FPGA met VHDL. PWM heeft een vaste frequentie en een variabele spanning. Dit artikel bespreekt ook de Digital Clock Manager voor het verlagen van de klokfrequentie door de scheefheid van het kloksignaal te verminderen. Een vaste frequentie wordt gebruikt om de invoergegevens te produceren die de PWM-signalen produceren met behulp van een comparator. Elektronische bedrijven ontwerpen de hardware die voor hun producten is bedoeld met hun standaarden en protocollen, waardoor het voor de eindgebruikers een uitdaging wordt om de hardware opnieuw te configureren volgens hun behoeften. Deze behoefte aan hardware heeft geleid tot de groei van een nieuw segment van klant-configureerbaar in het veld programmeerbare geïntegreerde schakelingen genaamd FPGA's

Pulsbreedtemodulatie (PWM)

Pulsbreedtemodulatie wordt veel gebruikt in toepassingen van communicatie en controlesystemen Pulsbreedtemodulatie kan worden gegenereerd met behulp van verschillende benaderingen in besturingssystemen. Hier, in dit artikel, wordt PWM gegenereerd met behulp van Hardware Description Language (VHDL) en geïmplementeerd op FPGA. Implementatie van PWM op FPGA kan de gegevens sneller verwerken en de controllerarchitectuur kan worden geoptimaliseerd voor ruimte of snelheid.

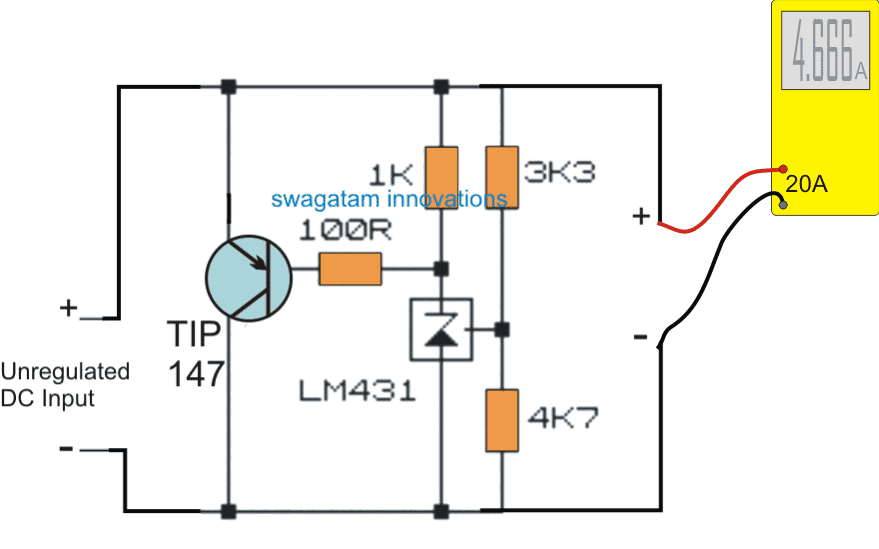

PWM is een techniek om gedurende een gecontroleerde tijdsperiode logische ‘0’ en logische ‘1’ te bieden. Het is een signaalbron die de modulatie van zijn duty-cycle omvat om de hoeveelheid stroom die naar de belasting wordt gestuurd te regelen. In PWM wordt de tijdsperiode van de blokgolf constant gehouden en wordt de tijd gedurende welke het signaal HOOG blijft gevarieerd.

De PWM genereert de pulsen op zijn uitgang zodanig dat de gemiddelde waarde van HIGHs en LOWs evenredig is met de PWM-ingang. De duty-cycle van het signaal kan worden gevarieerd. Een PWM-signaal is een blokgolf met een constante periode en een variërende duty-cycle. Dat wil zeggen, de frequentie van het PWM-signaal is constant, maar de tijdsperiode van het signaal blijft hoog en varieert zoals weergegeven.

PWM-signaal

VHDL

VHDL is een taal die wordt gebruikt om het gedrag van digitale circuitontwerpen VHDL wordt gebruikt door industrieën en academici voor simulatie van digitale schakelingen. Het ontwerp kan worden gesimuleerd en vertaald in de vorm die geschikt is voor implementatie in hardware.

PWM-architectuur

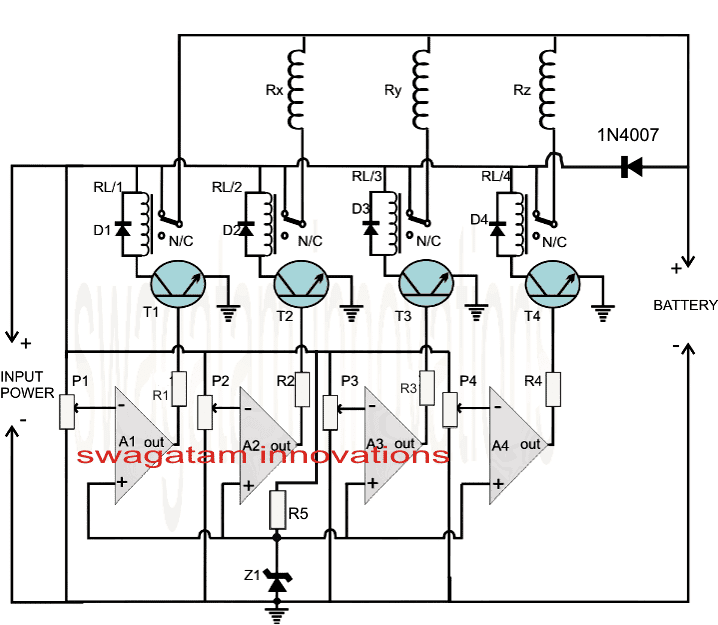

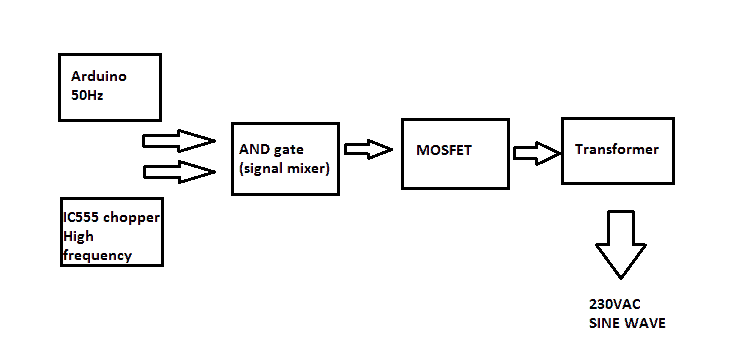

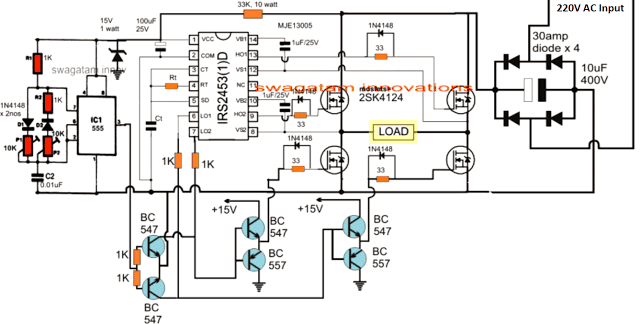

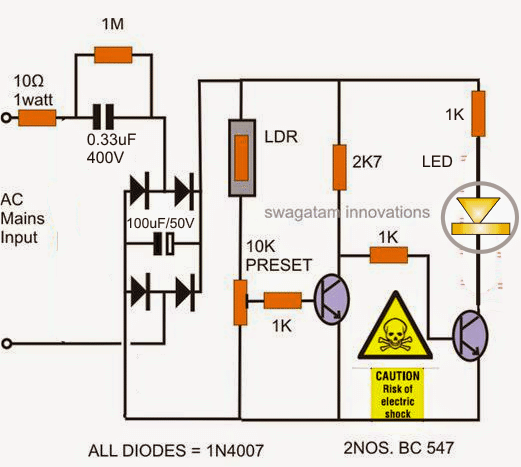

Om de invoergegevens te produceren om de PWM te genereren met behulp van een snelle N-bit vrijlopende teller, waarvan de uitvoer wordt vergeleken met de registeruitvoer en de gewenste invoerwerkcyclus opslaat met behulp van een comparator. De vergelijker output is ingesteld op 1 als deze beide waarden gelijk zijn. Deze comparatoruitgang wordt gebruikt om RS-latch in te stellen. Het overloopsignaal van de teller wordt gebruikt om de RS-vergrendeling te resetten. De output van RS latch geeft de gewenste PWM-output. Dit overloopsignaal wordt ook gebruikt om een nieuwe N-bit duty-cycle in het register te laden. PWM heeft een vaste frequentie en een variabele spanning. Deze spanningswaarde verandert van 0V naar 5 V.

PWM-signaal met variabele duty-cycle

De basis-PWM genereert de signalen, die de uitvoer van PWM geven, vereist een comparator die twee waarden vergelijkt. De eerste waarde vertegenwoordigt het kwadraat-signaal dat wordt gegenereerd door de N-bit-teller en de tweede waarde vertegenwoordigt het kwadraat-signaal dat de informatie over de duty-cycle bevat. De teller genereert het laadsignaal wanneer er een overloop is. Zodra het laadsignaal actief wordt, laadt het register de nieuwe duty cycle-waarde. Het laadsignaal wordt ook gebruikt om de grendel te resetten. Latch-uitgang is een PWM-signaal. Dit hangt af van de verandering in de duty-cycle-waarde.

Wat is FPGA?

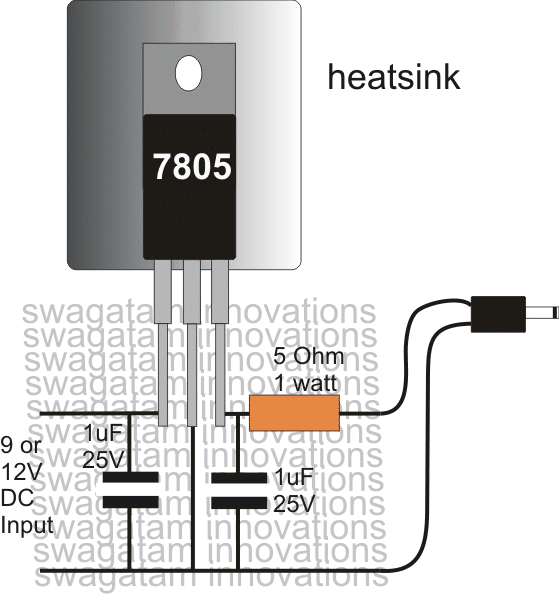

De FPGA is een veld-programmeerbare poortopstelling. Het is een type apparaat dat veel wordt gebruikt in elektronische schakelingen. FPGA's zijn halfgeleiderinrichtingen die programmeerbare logische blokken en verbindingsschakelingen bevatten. Het kan na fabricage worden geprogrammeerd of opnieuw worden geprogrammeerd naar de vereiste functionaliteit.

FPGA

Basisprincipes van FPGA

Wanneer een printplaat is vervaardigd en of deze een FPGA als onderdeel ervan bevat. Dit wordt tijdens het fabricageproces geprogrammeerd en kan later opnieuw worden geprogrammeerd om een update te maken of de nodige wijzigingen aan te brengen. Deze functie van FPGA maakt het uniek ten opzichte van ASIC. Toepassingsspecifieke geïntegreerde schakelingen (ASIC) worden op maat vervaardigd voor specifieke ontwerptaken. In het verleden werden FPGA's gebruikt om een ontwerp met lage snelheid, complexiteit en volume te ontwikkelen, maar tegenwoordig zal FPGA de prestatiebarrière gemakkelijk opdrijven tot 500 MHz.

In microcontrollers is de chip ontworpen voor een klant en zij moeten de software schrijven en deze compileren tot hex-bestand om op de microcontroller te laden. Deze software kan eenvoudig worden vervangen omdat deze is opgeslagen in het flash-geheugen. In FPGA's is er geen processor om de software uit te voeren en wij zijn degene die het circuit ontwerpen. We kunnen een FPGA zo eenvoudig configureren als een EN-poort of een complex als een multi-coreprocessor. Om een ontwerp te maken, schrijven we Hardware Description Language (HDL), die uit twee typen bestaat: Verilog en VHDL. Vervolgens wordt de HDL gesynthetiseerd in een bitbestand met behulp van een BITGEN om de FPGA te configureren. De FPGA slaat de configuratie op in RAM, dat wil zeggen dat de configuratie verloren gaat als er geen stroomaansluiting is. Daarom moeten ze elke keer dat er stroom wordt geleverd, worden geconfigureerd.

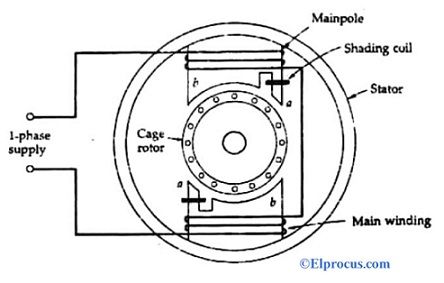

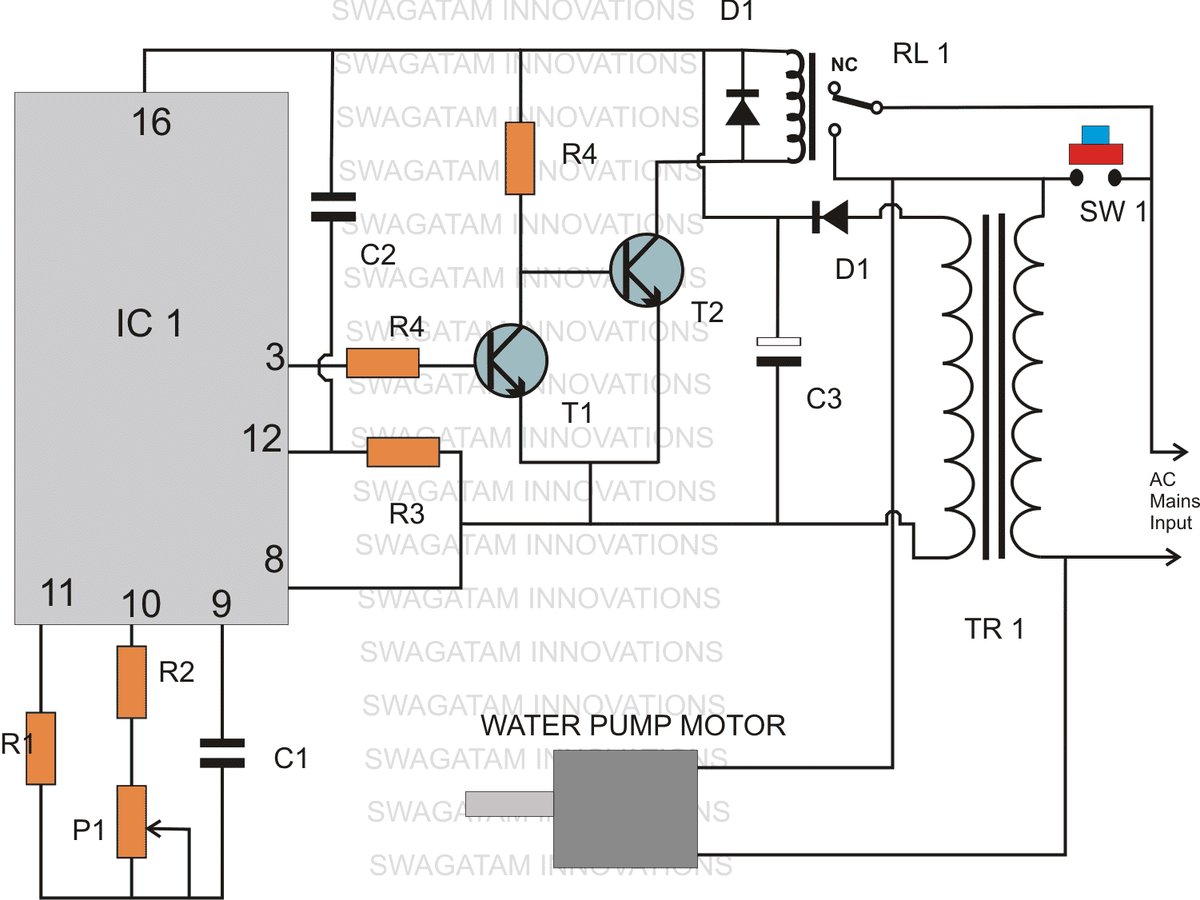

Architectuur van FPGA

FPGA's zijn geprefabriceerde siliciumchips die elektrisch kunnen worden geprogrammeerd om digitale ontwerpen te implementeren. De eerste op statisch geheugen gebaseerde FPGA genaamd SRAM wordt gebruikt voor het configureren van zowel logica als interconnectie met behulp van een stroom configuratiebits. De moderne EPGA van vandaag bevat ongeveer 3.30.000 logische blokken en ongeveer 1.100 inputs en outputs.

FPGA-architectuur

De architectuur van FPGA bestaat uit drie hoofdcomponenten

- Programmeerbare logische blokken, die logische functies implementeren

- Programmeerbare routing (interconnects), die functies implementeert

- I / O-blokken, die worden gebruikt om off-chip verbindingen te maken

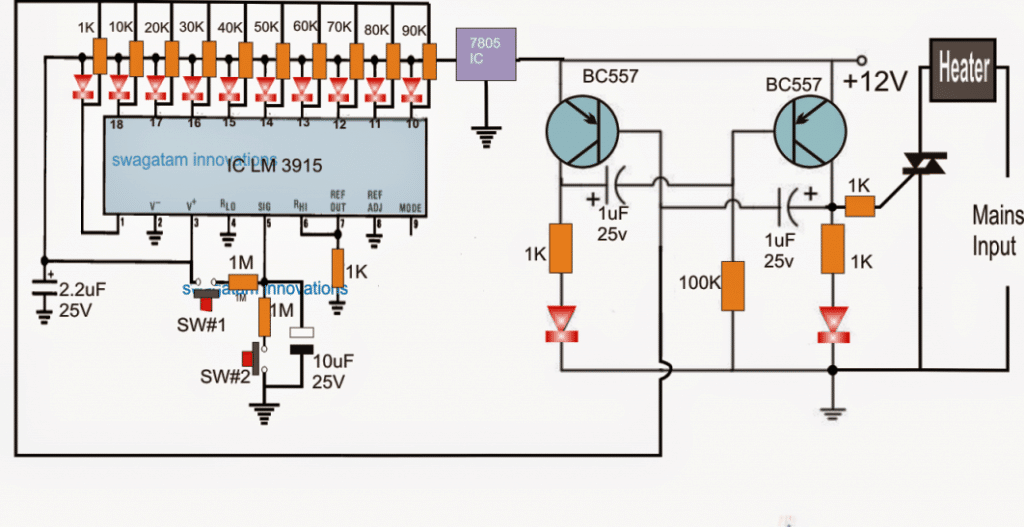

Toepassingen van PWM-signalen

PWM-signalen worden veel gebruikt voor besturingstoepassingen. Zoals het aansturen van gelijkstroommotoren, regelkleppen, pompen, hydraulica, etc. Hier zijn de weinige toepassingen van de PWM-signalen.

- Verwarmingssystemen met langzame tijden 10 tot 100Hz of hoger.

- DC-elektromotoren 5 tot 10 KHz

- Voedingen of audioversterkers 20 tot 200 KHz.

Dit artikel gaat helemaal over de generatie van PWM-signalen met variabele inschakelduur met FPGA. Bovendien kunt u voor hulp bij elektronische projecten of twijfels over dit artikel contact met ons opnemen door te reageren op het commentaargedeelte hieronder.