Vermenigvuldigers worden gebruikt in een breed scala van digitale signaalverwerking en andere toepassingen. Vanwege de vooruitgang in de huidige technologieën hebben veel onderzoekers zich voornamelijk geconcentreerd op de ontwerpfactoren, voor betere prestaties. Enkele van de ontwerpdoelen zijn: hoge snelheid, nauwkeurigheid, laag stroomverbruik, regelmaat van lay-out, minder oppervlakte. DSP-processor heeft verschillende rekenblokken, zoals multiplexers, adders, MAC De snelheid van werking en uitvoering van deze blokken is verbeterd in vergelijking met eerdere versies. De uitvoeringssnelheid van vermenigvuldigers is afhankelijk van twee factoren, halfgeleidertechnologie , en multiplier-architectuur. Adders zijn de basisbouwsteen van digitale multiplexers, waar we een reeks herhaalde toevoegingen uitvoeren, om de vermenigvuldigingsbewerking te versnellen, moet de bewerkingssnelheid van de opteller worden verhoogd. Er zijn veel toepassingen voor digitale signaalverwerking, waarbij het kritieke vertragingspad en de prestaties van de processor in de vermenigvuldiger liggen. Er zijn verschillende soorten vermenigvuldigers, waarvan de 4 × 4 array-vermenigvuldiger een geavanceerde is die in dit artikel wordt beschreven.

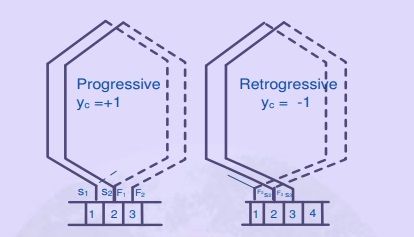

Vermenigvuldigingsregelingen in 4 × 4 Array Multiplier

Er zijn twee soorten vermenigvuldigingsschema's

Seriële vermenigvuldiging (Shift – Toevoegen): De seriële vermenigvuldiging kan worden opgelost door deelproducten te zoeken en vervolgens deelproducten bij elkaar op te tellen. De implementaties zijn primitief met een eenvoudige architectuur

Parallelle vermenigvuldiging: De parallelle producten worden gelijktijdig gegenereerd in parallelle vermenigvuldiging en een krachtige machine. Parallelle implementaties worden toegepast, latentie wordt geminimaliseerd.

Vermenigvuldigingsalgoritme

Het vermenigvuldigingsproces bestaat uit drie hoofdstappen:

- Gedeeltelijke productgeneratie

- Gedeeltelijke productreductie

- Laatste toevoeging.

De gebruikelijke vermenigvuldigingsmethode is het 'optellen en verschuiven' -algoritme. Het vermenigvuldigingsalgoritme voor een N-bit-vermenigvuldiger wordt hieronder weergegeven.

4-bij-4-vermenigvuldiging

4 - met - 4 - vermenigvuldiging 1

voorbeeld-2

Deelproducten worden gegenereerd met EN-poorten, waar

- Multiplicand = N-bits

- Vermenigvuldiger = M-bits

- deelproducten = N * M.

De vermenigvuldiging van twee 8-bits getallen, die het 16-bits product genereert.

De optelling is

P (m + n) = EEN (m). B (n) = ik = 0 m-1∑ j = 0n-1∑ ai bj 2i + j ……. 1

A, B = 8 bits

Stappen in vermenigvuldiging

Hieronder volgen de stappen voor elke vermenigvuldiging

- Als LSB van Multiplier ‘1’ is. voeg dan het vermenigvuldigingsband toe aan een accumulator. vermenigvuldigingsbit wordt één bit naar rechts verschoven en het vermenigvuldigingsbit wordt één bit naar links verschoven.

- Stop als alle bits van de vermenigvuldiger nul zijn.

- Er wordt minder hardware gebruikt als deelproducten serieel worden toegevoegd. We kunnen alle PP optellen door een parallelle vermenigvuldiger. Het is echter mogelijk om compressietechniek te gebruiken, het aantal deelproducten kan worden verminderd voordat de toevoeging wordt uitgevoerd.

Verschillende soorten multipliers

De verschillende soorten vermenigvuldigers zijn,

Booth-multiplier

De functie van de vermenigvuldiger van het hokje is het vermenigvuldigen van 2 ondertekende binaire getallen die worden weergegeven in 2-complement het formulier. De voordelen van standsvermenigvuldigers zijn Minimaal complex, Vermenigvuldiging wordt versneld. De nadelen van standvermenigvuldigers zijn dat het stroomverbruik hoog is.

Combinationele multiplier

De combinationele vermenigvuldiger voert een vermenigvuldiging uit van twee niet-ondertekende binaire getallen. Het voordeel van een combinatievermenigvuldiger is dat deze gemakkelijk tussenproducten kan genereren. Het belangrijkste nadeel van de combinatievermenigvuldiger is dat deze grote gebieden beslaat.

Sequentiële vermenigvuldiger

Vermenigvuldiging wordt opgedeeld in de opeenvolging van stappen, waarbij het gegenereerde deelproduct wordt opgeteld bij de accumulator. De deelsom wordt nu naar de volgende stap verschoven. Het voordeel hiervan is dat het minder ruimte inneemt. Het nadeel van een sequentiële vermenigvuldiger is dat het een langzaam proces is.

Wallace-boomvermenigvuldiger

Het vermindert het aantal deelproducten en gebruikt een selectieve toevoeging voor de toevoeging van deelproducten. Het voordeel van de Wallace-boomvermenigvuldiger is een hoge snelheid en een gemiddeld complex ontwerp. Het grootste nadeel van Wallace-boomvermenigvuldiger is dat het lay-outontwerp onregelmatig is en een groter gebied inneemt.

Array-multiplier

Het vermenigvuldigingscircuit is gebaseerd op het algoritme voor verschuiving toevoegen. Het belangrijkste voordeel van de arrayvermenigvuldiger is dat deze eenvoudig is qua ontwerp en regelmatig van vorm is. Het nadeel van een arrayvermenigvuldiger is dat de vertraging hoog en hoog stroomverbruik is.

Shift en Multiplier toevoegen

Het is vergelijkbaar met het normale vermenigvuldigingsproces, dat we in de wiskunde doen, van arrayvermenigvuldigingsstroomchat waarbij X = Multiplicand Y = Multiplier A = Accumulator, Q = Quotiënt. Eerst wordt Q gecontroleerd of het 1 is of niet als het 1 is, voeg dan A en B toe en verschuif A_Q rekenkundig naar rechts, anders als het niet 1 is, verschuif A_Q rekenkundig direct naar rechts en verlaag N met 1, controleer in de volgende stap of N 0 is of niet. Als N niet 0 wordt herhaald vanaf Q = 0, beëindig anders het proces.

shift-and-add-multiplier

Constructie en werking van een 4 × 4 Array Multiplier

De ontwerpstructuur van de array-multiplier is regelmatig, het is gebaseerd op het principe van het algoritme voor het toevoegen van verschuivingen.

Gedeeltelijk product = het multiplicand * vermenigvuldigingsbit ………. (2)

waar EN-poorten worden gebruikt voor het product, wordt de optelling gedaan met behulp van Full Adders en Half Adders, waarbij het deelproduct wordt verschoven volgens hun bitvolgorde. In een n * n array-vermenigvuldiger berekenen n * n AND-poorten de partiële producten en kan de toevoeging van partiële producten worden uitgevoerd met n * (n - 2) Full-optellers en n Half-optellers. De getoonde 4 × 4 array-multiplier heeft 8 inputs en 8 outputs

4-bij-4-array-multiplier

Bouwstenen van 4 × 4 Array Multiplier

Een volledige opteller heeft drie invoerlijnen en twee uitvoerlijnen, waar we dit gebruiken als een basisbouwsteen van een arrayvermenigvuldiger. Het volgende is het voorbeeld van een 4 × 4 array-multiplier. Het meest linkse bit is het LSB-bit van een deelproduct.

adder-blokschema

array-multiplier-blokschema

Het meest rechtse bit is het MSB-bit van een deelproduct. De deelproducten worden nu bij vermenigvuldiging naar de linkerkant verschoven en worden toegevoegd om het eindproduct te krijgen. Dit proces wordt herhaald totdat er geen twee deelproducten meer naar buiten komen voor toevoeging.

4-bij-4-vermenigvuldiging-1

logic-diagram-of-4-by-4 - array - multiplier

Waar a0, a1, a2, a3 en b0, b1, b2, b3 Multiplicand en Multiplier zijn, is de optelling van alle producten deelproducten. Het resultaat van de som van het deelproduct is een product.

Voor een 4 × 4 array-multiplier heeft deze 16 EN-poorten, 4 halve adders (HA's) en 8 volledige adders (FA's) nodig. Totaal 12 adders.

Voordelen van 4 × 4 Array Multiplier

De voordelen van array-multiplier zijn,

- Minimale complexiteit

- Gemakkelijk schaalbaar

- Gemakkelijk pijplijn

- Regelmatige vorm, gemakkelijk te plaatsen en te routeren

Nadelen van 4 × 4 Array Multiplier

De nadelen van een arrayvermenigvuldiger zijn als volgt,

- Hoog stroomverbruik

- Meer digitale poorten resulterend in grote gebieden.

Toepassingen van 4 × 4 Array Multiplier

De toepassingen van array-multiplier worden vermeld,

- Array-multiplier wordt gebruikt om de rekenkundige bewerking , zoals filteren, Fourier-transformatie, beeldcodering.

- Hoge snelheid.

Dit gaat dus allemaal over 4 × 4 array-vermenigvuldiger Dit is een geavanceerde vermenigvuldiger gebaseerd op het principe van toevoegen en verschuiven, de prestaties kunnen eenvoudig worden verhoogd met behulp van de pijplijntechniek met een eenvoudige constructie, hoewel het meer logische poorten gebruikt waar het kan worden geïmplementeerd met Verilog. Hier is een vraag: 'Hoeveel logische poorten zijn er nodig om een 3 * 3 array-vermenigvuldiger te ontwerpen?'.